#### **MD Decoder IC**

#### Overview

The LC896431 implements playback signal processing that conforms to the MiniDisc format standards. This device was designed to form a chip set in conjunction with a SANYO RF amplifier IC.

#### **Features**

- Fabricated in a CMOS process for low power

- An application system can be created easily by combining this IC with a SANYO RF amplifier IC.

- Provides digital servo functions and a VCEC for highspeed access.

- Allows the creation of optimal systems by integrating 8× oversampling digital filters, a 1-bit D/A converter, and a low-pass filter on the same chip.

#### **Functions**

- Full complement of automatic adjustment functions

- · Intensity, defect, and shock detection

- · Both CLV and CAV control

- VCEC circuit

- · Automatic adjustment functions

- High-performance ATRAC3 decoder

- · EFM data demodulation

- Error detection and correction (C1: E12, C2: E24)

- Error correction RAM

- Intelligent commands

- · Anti-shock control

- · ADIP demodulation and decoding

- · Digital servo

- · EFM ACIRC decoding

- High-performance 1-bit D/A converter

- Built-in second-order low-pass filter for audio output

- Power saving function for the stopped and paused states

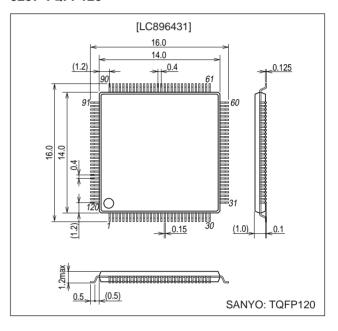

## **Package Dimensions**

unit: mm

#### 3257-TQFP120

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

## **Specifications**

# Maximum Ratings at $V_{SS} = 0~V$

| Parameter S                 |                                 | Conditions | Ratings               | Unit |

|-----------------------------|---------------------------------|------------|-----------------------|------|

| Supply voltage              | V <sub>DD1</sub> max            |            | 2.7                   | V    |

| Supply voltage              | V <sub>DD2</sub> max            |            | 2.7                   | V    |

| Input and output voltage    | V <sub>I</sub> , V <sub>O</sub> |            | 0 to V <sub>DD2</sub> | V    |

| Operating temperature *1    | Topr                            |            | -10 to +70            | °C   |

| Storage temperature         | Tstg                            |            | -55 to +125           | °C   |

| Input and output current *2 | I <sub>I</sub> , I <sub>O</sub> |            | ±20                   | mA   |

Notes: 1. Does not guarantee continuous operation.

2. Maximum output current that flows constantly (except OUTL, OUTR, SLC0, PD0 pins)

#### Allowable Operating Ranges at $Ta = -10^{\circ}C$ to $+70^{\circ}C$ , $V_{SS} = 0$ V

In case of external I/O power supply,  $V_{DD2} = 2.3 \text{ V}$

| Parameter      |              | Symbol            | Symbol Conditions — | Ratings |     |     | Unit  |

|----------------|--------------|-------------------|---------------------|---------|-----|-----|-------|

|                |              | Symbol            |                     | min     | typ | max | Offic |

| Supply voltage | External I/O | $V_{DD2}$         |                     | 2.2     | 2.3 | 2.4 |       |

|                | Internal     | V <sub>DD</sub>   |                     | 1.5     | 1.6 | 1.8 |       |

|                |              | AV <sub>DD</sub>  |                     | 2.2     | _   | 2.6 | V     |

|                |              | AV <sub>DD1</sub> |                     | 2.2     | _   | 2.6 |       |

|                |              | VCV <sub>DD</sub> |                     | 2.2     | _   | 2.6 |       |

In case of external I/O power supply,  $V_{DD2} = 2.5 \text{ V}$

| Parameter      |              | Symbol            | Conditions | Ratings |     |      | Unit  |

|----------------|--------------|-------------------|------------|---------|-----|------|-------|

|                |              | Symbol            | Conditions | min     | typ | max  | Offic |

|                | External I/O | $V_{DD2}$         |            | 2.2     | 2.5 | 2.55 |       |

| Supply voltage | Internal     | $V_{DD}$          |            | 1.55    | 1.6 | 1.80 |       |

|                |              | $AV_{DD}$         |            | 2.2     | _   | 2.6  | V     |

|                |              | AV <sub>DD1</sub> |            | 2.2     | _   | 2.6  |       |

|                |              | VCV <sub>DD</sub> |            | 2.2     | _   | 2.6  |       |

Notes: 1. Supply all power supplies at less than the maximum gradient of 0.4 V/ms, and implement a delay of 10 ms or longer for current to go from 0 V to

- 2. Supply all power supplies simultaneously so that there are no delay differences among them.

- 3. Supply 0 to the RESETB pin only upon power application, and following power application, supply 1 and use with this value.

#### **Electrical Characteristics**

#### DC characteristics

## Input/output level: at Ta = -10 to $70^{\circ}$ C, $V_{SS} = 0$ V, $V_{DD1} = 1.5$ to 1.8 V, $V_{DD2} = 2.2$ to 2.55 V

| Parameter                 | Cumbal          | Conditions                          |                       |     |                            | Unit  |

|---------------------------|-----------------|-------------------------------------|-----------------------|-----|----------------------------|-------|

| Farameter                 | Symbol          | Conditions                          | min                   | typ | max                        | Offic |

|                           |                 | Except *1 to *3                     | $V_{DD2} \times 0.75$ | _   | _                          |       |

| Input high-level voltage  | V <sub>IH</sub> | *1                                  | $V_{DD2} \times 0.80$ | 1   | _                          | V     |

|                           |                 | *2                                  | $V_{DD2}/2 + 0.10$    | -   | $V_{DD2}$                  |       |

|                           |                 | Except *1 to *3                     | _                     | -   | $V_{DD2} \times 0.25$      |       |

| Input low-level voltage   | V <sub>IL</sub> | *1                                  | _                     | -   | $V_{DD2} \times 0.20$      | V     |

|                           |                 | *2                                  | V <sub>SS</sub>       | _   | V <sub>DD2</sub> /2 – 0.10 |       |

| Output high-level voltage | V <sub>OH</sub> | I <sub>OH2</sub> = -1 mA, Except *4 | $V_{DD2} \times 0.80$ | 1   | _                          | V     |

| Output low-level voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 1 mA, Except *4   | _                     | l   | $V_{DD2} \times 0.15$      | V     |

| Output leakage current    | I <sub>OZ</sub> | *5                                  | -10.0                 | -   | 10.0                       | μΑ    |

| Pull-up resistance        | R <sub>UP</sub> |                                     | 46                    | 100 | 270                        | kΩ    |

Notes: \*1: CL, CE, RESETB, ADIPWO, HFL

- \*2: EFMIN

- \*3: PEAK, BOTTOM, ABCD, TE, FE, VC

- \*4: OUTL, OUTR

- \*5: During high-impedance output. Current also flows through pull-up resistance for MD3 to 0.

- XIN, XOUT, SLC0, and PD0 are not included in DC characteristics

- The FR, ISET, SLCIST bias resistance pins are not included in DC characteristics.

# Analog characteristics

Input/output level: at Ta = -10 to  $+70^{\circ}$ C,  $V_{SS} = 0$  V,  $V_{DD1} = 2.2$  to 2.6 V

| Parameter              | Symbol | Conditions                     | Ratings               |     |                       | Unit |

|------------------------|--------|--------------------------------|-----------------------|-----|-----------------------|------|

|                        | Symbol | Conditions                     | min typ               | max |                       |      |

| Analog input voltage   | VI     | PEAK, BOTTOM, ABCD, TE, FE, VC | $AV_{DD1} \times 0.2$ | _   | $AV_{DD1} \times 0.8$ | V    |

| Input load capacitance |        | PEAK, BOTTOM, ABCD, TE, FE, VC | _                     | _   | 7.5                   | pF   |

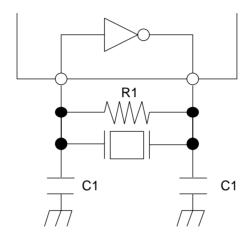

## Oscillation amplifier

Note: Xtal is limited to the basic mode.

## **Pin Functions**

$I/O \rightarrow I$ : Input pin, O: Output pin, B: Bidirectional pin

Note: Do not leave  $V_{DD}$  and  $V_{SS}$  open, connect all to power supply, ground.

| Pin No. | Pin Name                | I/O     | Function                                                    |

|---------|-------------------------|---------|-------------------------------------------------------------|

| 1       | V <sub>DD2</sub>        | _       | Power supply pin                                            |

| 2       | SHOCK                   | 0       | SHOCK/RFNG output pin                                       |

| 3       | SLCO                    | 0       | HF signal slice level output pin                            |

| 4       | SLCIST                  | I       | Bias resistance pin of slice level adjustment amplifier     |

| 5       | EFMIN                   | I       | HF signal input pin                                         |

| 6       | RESETB                  | I       | System reset                                                |

| 7       | HFL                     | I       | Track detection signal input pin                            |

| 8       | TEST2                   | I       | Test input pin                                              |

| 9       | PDO                     | 0       | VCEC current charge pump output pin                         |

| 10      | VCV <sub>SS</sub>       | _       | VCEC ground pin                                             |

| 11      | FR                      | 1       | Bias resistance pin for oscillation frequency of VCEC       |

| 12      | ISET                    | ı       | Bias resistance pin for current charge pump of VCEC         |

| 13      | VCV <sub>DD</sub>       | _       | VCEC power supply pin                                       |

| 14      | AV <sub>SS1</sub>       | _       | Digital servo ground pin                                    |

| 15      | PEAK                    | ı       | PEAK signal input pin                                       |

| 16      | BOTTOM                  | ı       | BOTTOM signal input pin                                     |

| 17      | ABCD                    | I       | Main beam light intensity signal input pin                  |

| 18      | TE                      | I       | Tracking error signal input pin                             |

| 19      | FE                      | ı       | Focus error signal input pin                                |

| 20      | VC                      | ·       | Midpoint potential input pin                                |

| 21      | AV <sub>DD1</sub>       | _       | Digital servo power supply pin                              |

| 22      | DSW1                    | B*      | Disk mode switch output                                     |

| 23      | DSW0                    | B*      | Disk mode switch output                                     |

| 24      | SGC                     | B*      | AGC control signal output pin                               |

| 25      | AOFFSET                 | B*      | ABCD offset control signal output pin                       |

| 26      | FOFFSET                 | B*      | Focus offset control signal output pin                      |

| 27      | TOFFSET                 | B*      | Tracking offset control signal output pin                   |

| 28      | TBAL                    | B*      | Tracking bilance control signal output pin                  |

| 29      | LDREF                   | B*      | Laser control signal output pin                             |

| 30      |                         |         | Ground pin                                                  |

| 31      | V <sub>SS</sub>         |         | ·                                                           |

| 32      | V <sub>DD</sub><br>FBAL | —<br>B* | Internal power supply pin  Focus balance control output pin |

| 33      | SPPWMF                  | B*      |                                                             |

|         |                         | B*      | Spindle PWM output pin                                      |

| 34      | SPPWMR                  |         | Spindle PWM output pin                                      |

| 35      | MD7                     | В       | DRAM data input/output pin                                  |

| 36      | MD6                     | В       | DRAM data input/output pin                                  |

| 37      | MD5                     | В       | DRAM data input/output pin                                  |

| 38      | MD4                     | В       | DRAM data input/output pin                                  |

| 39      | V <sub>DD2</sub>        |         | Power supply pin                                            |

| 40      | MD3                     | В       | DRAM data input/output pin                                  |

| 41      | MD2                     | В       | DRAM data input/output pin                                  |

| 42      | MD1                     | В       | DRAM data input/output pin                                  |

| 43      | MD0                     | В       | DRAM data input/output pin                                  |

| 44      | PCK                     | 0       | VCEC system clock signal output pin                         |

| 45      | V <sub>DD2</sub>        | _       | Power supply pin                                            |

| 46      | V <sub>SS</sub>         | _       | Ground pin                                                  |

| 47      | DEFECT                  | B*      | Defect signal input/output pin                              |

| 48      | MD15                    | В       | DRAM data input/output pin                                  |

| 49      | MD14                    | В       | DRAM data input/output pin                                  |

| 50      | MD13                    | В       | DRAM data input/output pin                                  |

| 51      | MD12                    | В       | DRAM data input/output pin                                  |

| 52      | V <sub>SS</sub>         |         | Ground pin                                                  |

| 53      | MD11                    | В       | DRAM data input/output pin                                  |

Continued on next page.

Continued from preceding page.

| Pin No. | Pin Name                           | I/O      | Function                                             |

|---------|------------------------------------|----------|------------------------------------------------------|

| 54      | MD10                               | В        | DRAM data input/output pin                           |

| 55      | MD9                                | В        | DRAM data input/output pin                           |

| 56      | MD8                                | В        | DRAM data input/output pin                           |

| 57      | SLPWMF                             | B*       | Sled PWM output pin                                  |

| 58      | SLPWMR                             | B*       | Sled PWM output pin                                  |

| 59      | SLD0                               | B*       | Sled control signal output pin                       |

| 60      | V <sub>SS</sub>                    | _        | Ground pin                                           |

| 61      | V <sub>DD2</sub>                   |          | Power supply pin                                     |

| 62      | SLD1                               | В        | Sled control signal input/output pin                 |

| 63      | V <sub>DD</sub>                    |          | Internal power supply pin                            |

| 64      | SLD2                               |          | Sled control signal input pin                        |

| 65      | SLD3                               | i        | Sled control signal input pin                        |

| 66      | FOPWMF                             | <br>B*   | Focus PWM output pin                                 |

| 67      | FOPWMR                             | B*       | Focus PWM output pin                                 |

|         | TRPWMF                             | B*       |                                                      |

| 68      |                                    |          | Tracking PWM output pin                              |

| 69      | TRPWMR                             | B*       | Tracking PWM output pin                              |

| 70      | FG                                 | I        | Speed pulse input pin                                |

| 71      | VP                                 | B*       | CLV servo lock judgment output pin                   |

| 72      | FOK                                | B*       | Focus OK signal output pin                           |

| 73      | FAST                               | B*       | FAST signal output pin                               |

| 74      | CL                                 | ı        | CPU interface data transfer clock input pin          |

| 75      | CE                                 | l        | CPU interface chip enable signal input pin           |

| 76      | DI                                 | I        | CPU interface data input pin                         |

| 77      | DO                                 | 0        | CPU interface data output pin                        |

| 78      | WRQB                               | 0        | CPU interface interrupt signal output pin            |

| 79      | INTB                               | 0        | CPU interface interrupt signal output pin            |

| 80      | FSEQ                               | B*       | Frame synchronization detection signal output pin    |

| 81      | F16M                               | B*       | 16.9344 MHz output pin                               |

| 82      | ENH                                | B*       | De-emphasis specification output pin                 |

| 83      | LRCO                               | B*       | LR clock output pin                                  |

| 84      | DDATA                              | B*       | Speech signal data output pin                        |

| 85      | BCO                                | B*       | Bit clock output pin                                 |

| 86      | DDOUT (DEFECT)                     | B*       | Digital audio output pin                             |

| 87      | V <sub>DD2</sub>                   | _        | Power supply pin                                     |

| 88      | XIN                                | I        | 16.9344 MHz oscillation input pin                    |

| 89      | XOUT                               | 0        | 16.9344 MHz oscillation output pin                   |

| 90      | V <sub>SS</sub>                    | _        | Ground pin                                           |

| 91      | V <sub>DD</sub>                    | _        | Internal power supply pin                            |

| 92      | AV <sub>SS</sub>                   | _        | 1-bit DAC ground pin                                 |

| 93      | OUTR                               | 0        | 1-bit DAC right channel output pin                   |

| 94      | OUTL                               | 0        | 1-bit DAC left channel output pin                    |

| 95      | AV <sub>DD</sub>                   |          | 1-bit DAC power supply pin                           |

| 96      | MCASB                              | B*       | DRAM CAS signal output pin                           |

| 97      | MOEB                               | B*       | DRAM OE signal output pin                            |

| 98      | MAD9                               | B*       | DRAM address output pin                              |

| 99      | MAD8                               | B*       | DRAM address output pin                              |

| 100     | MAD7                               | B*       | DRAM address output pin                              |

| 100     | TEST1                              | I        | Test input pin                                       |

| 101     | MAD6                               | B*       | DRAM address output pin                              |

| 102     |                                    | B*       |                                                      |

|         | MAD4                               |          | DRAM address output pin                              |

| 104     | MAD4                               | B*       | DRAM address output pin                              |

| 105     | TEST3                              | I        | Test input pin                                       |

| 106     | V <sub>SS</sub>                    |          | Ground pin                                           |

|         |                                    |          |                                                      |

| 107     | V <sub>DD2</sub>                   |          | Power supply pin                                     |

|         | V <sub>DD2</sub><br>SMON3<br>SMON2 | B*<br>B* | Monitor signal output pin  Monitor signal output pin |

Continued from preceding page.

| Pin No. | Pin Name        | I/O | Function                   |

|---------|-----------------|-----|----------------------------|

| 110     | MAD3            | B*  | DRAM address output pin    |

| 111     | MAD2            | B*  | DRAM address output pin    |

| 112     | MAD1            | B*  | DRAM address output pin    |

| 113     | MAD0            | B*  | DRAM address output pin    |

| 114     | SMON1           | B*  | Monitor signal output pin  |

| 115     | SMON0           | B*  | Monitor signal output pin  |

| 116     | MRASB           | B*  | DRAM RAS signal output pin |

| 117     | MWEB            | B*  | DRAM WE signal output pin  |

| 118     | ADIPWO          | I   | Wobble signal input pin    |

| 119     | $V_{DD}$        | _   | Internal power supply pin  |

| 120     | V <sub>SS</sub> | _   | Ground pin                 |

Note: \* Output/input only during testing. Normally output.

TEST1 to TEST3: Always use fixed to High.

MD3 to MD0: Pull-up I/O with resistor

- Specifications of any and all SANYO products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO products (including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Electric Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of January, 2001. Specifications and information herein are subject to change without notice.