# **JVC SERVICE MANUAL** MICRO COMPONENT MD SYSTEM

#### Contents

| Safety precaution             | 1-2  |

|-------------------------------|------|

| Preventing static electricity | 1-3  |

| Disassembly method            | 1-4  |

| Adjustment method             | 1-39 |

| Maintenance of MD pickup      | 1-47 |

| Pr | ocedures of changing the        |

|----|---------------------------------|

|    | MD pickup 1-47                  |

| Ma | aintenance of DVD pickup 1-48   |

| Pr | ocedures of changing the        |

|    | DVD pickup 1-48                 |

| De | escription of major ICs 1-49~88 |

|    |                                 |

## -Safety Precautions-

- 1. This design of this product contains special hardware and many circuits and components specially for safety purposes. For continued protection, no changes should be made to the original design unless authorized in writing by the manufacturer. Replacement parts must be identical to those used in the original circuits. Services should be performed by qualified personnel only.

- 2. Alterations of the design or circuitry of the product should not be made. Any design alterations of the product should not be made. Any design alterations or additions will void the manufacturer's warranty and will further relieve the manufacture of responsibility for personal injury or property damage resulting therefrom.

- 3. Many electrical and mechanical parts in the products have special safety-related characteristics. These characteristics are often not evident from visual inspection nor can the protection afforded by them necessarily be obtained by using replacement components rated for higher voltage, wattage, etc. Replacement parts which have these special safety characteristics are identified in the Parts List of Service Manual. Electrical components having such features are identified by shading on the schematics and by (A) on the Parts List in the Service Manual. The use of a substitute replacement which does not have the same safety characteristics as the recommended replacement parts shown in the Parts List of Service Manual may create shock, fire, or other hazards.

- 4. The leads in the products are routed and dressed with ties, clamps, tubings, barriers and the like to be separated from live parts, high temperature parts, moving parts and/or sharp edges for the prevention of electric shock and fire hazard. When service is required, the original lead routing and dress should be observed, and it should be confirmed that they have been returned to normal, after re-assembling.

- 5. Leakage currnet check (Electrical shock hazard testing)

After re-assembling the product, always perform an isolation check on the exposed metal parts of the product (antenna terminals, knobs, metal cabinet, screw heads, headphone jack, control shafts, etc.) to be sure the product is safe to operate without danger of electrical shock.

Do not use a line isolation transformer during this check.

Plug the AC line cord directly into the AC outlet. Using a "Leakage Current Tester", measure the leakage current from each exposed metal parts of the cabinet, particularly any exposed metal part having a return path to the chassis, to a known good earth ground. Any leakage current must not exceed 0.5mA AC (r.m.s.).

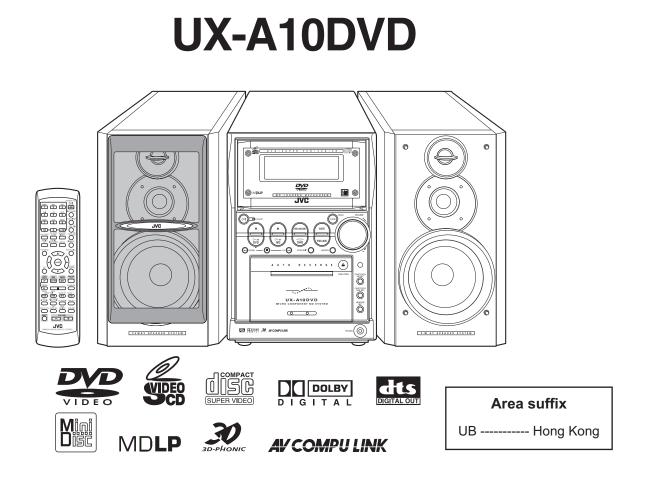

#### Alternate check method

Plug the AC line cord directly into the AC outlet. Use an AC voltmeter having, 1,000 ohms per volt or more sensitivity in the following manner. Connect a 1,500  $\Omega$  10W resistor paralleled by a 0.15 $\mu$ F AC-type capacitor

between an exposed metal part and a known good earth ground. Measure the AC voltage across the resistor with the AC voltmeter.

Move the resistor connection to each exposed metal part, particularly any exposed metal part having a return path to the chassis, and meausre the AC voltage across the resistor. Now, reverse the plug in the AC outlet and repeat each measurement. Voltage measured any must not exceed 0.75 V AC (r.m.s.). This corresponds to 0.5 mA AC (r.m.s.).

A CAUTION -

#### Warning

1. This equipment has been designed and manufactured to meet international safety standards.

2. It is the legal responsibility of the repairer to ensure that these safety standards are maintained.

- 3. Repairs must be made in accordance with the relevant safety standards.

- 4. It is essential that safety critical components are replaced by approved parts.

- 5. If mains voltage selector is provided, check setting for local voltage.

Burrs formed during molding may be left over on some parts of the chassis. Therefore, pay attention to such burrs in the case of preforming repair of this system.

In regard with component parts appearing on the silk-screen printed side (parts side) of the PWB diagrams, the parts that are printed over with black such as the resistor (-), diode (+) and ICP (-) or identified by the " $\Lambda$ " mark nearby are critical for safety.

(This regulation does not correspond to J and C version.)

# **Preventing static electricity**

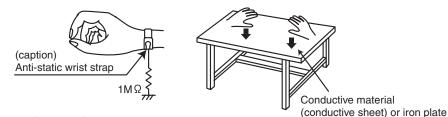

#### 1. Grounding to prevent damage by static electricity

Electrostatic discharge (ESD), which occurs when static electricity stored in the body, fabric, etc. is discharged, can destroy the laser diode in the traverse unit (optical pickup). Take care to prevent this when performing repairs.

#### 2.About the earth processing for the destruction prevention by static electricity

Static electricity in the work area can destroy the optical pickup (laser diode) in devices such as CD players. Be careful to use proper grounding in the area where repairs are being performed.

#### 2-1 Ground the workbench

Ground the workbench by laying conductive material (such as a conductive sheet) or an iron plate over it before placing the traverse unit (optical pickup) on it.

#### 2-2 Ground yourself

Use an anti-static wrist strap to release any static electricity built up in your body.

#### 3. Handling the optical pickup

- 1. In order to maintain quality during transport and before installation, both sides of the laser diode on the replacement optical pickup are shorted. After replacement, return the shorted parts to their original condition. (Refer to the text.)

- 2. Do not use a tester to check the condition of the laser diode in the optical pickup. The tester's internal power source can easily destroy the laser diode.

#### Attention when traverse unit is decomposed

# \*Please refer to "Disassembly method" in the text for pick-up and how to detach the substrate.

- 1.Solder is put up before the card wire is removed from connector on the CD substrate as shown in Figure. (When the wire is removed without putting up solder, the pick-up assembly might destroy.)

- 2.Please remove solder after connecting the card wire with when you install picking up in the substrate.

# **Disassembly method**

#### <Main body>

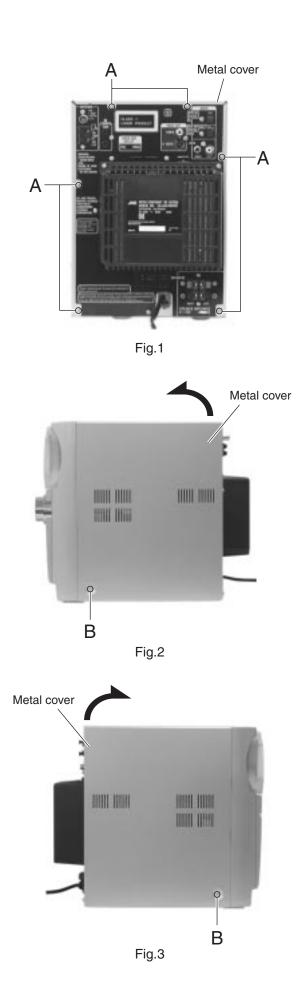

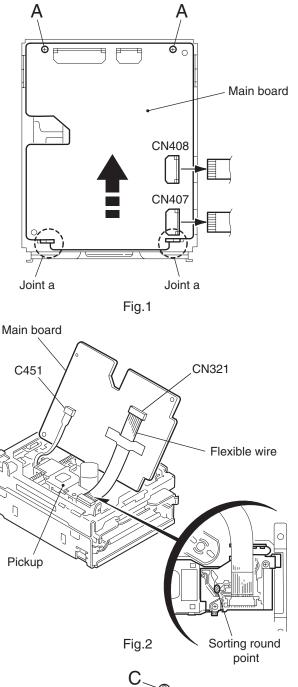

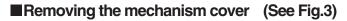

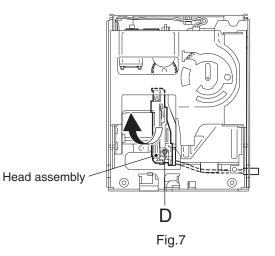

#### ■ Removing the metal cover (See Fig.1~3)

- 1. Remove the six screws **A** on the back of the body.

- 2. Remove the screw  $\, {\bf B}$  on each side of the body.

- 3. Detach the rear side of the metal cover upward while pulling the lower sides outward.

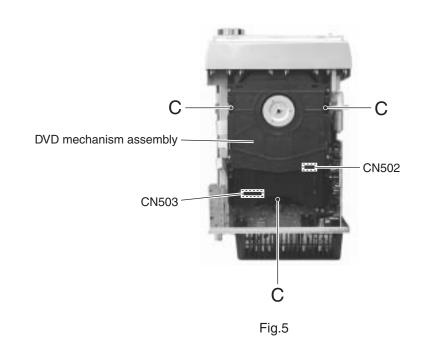

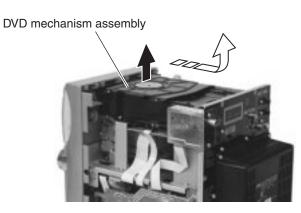

#### Removing the DVD mechanism assembly (See Fig.4~6)

- Prior to performing the following procedure, remove the metal cover.

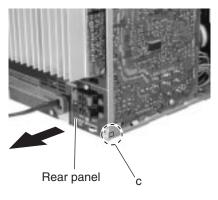

- 1. Remove the three screws **C** attaching the DVD mechanism assembly on top of the body.

- 2. Disconnect connector CN502 and CN503 on the DVD servo board upward at the bottom of the DVD mechanism assembly.

Bring up the DVD mechanism assembly and remove backward.

DVD mechanism assembly

Fig.4

Fig.6

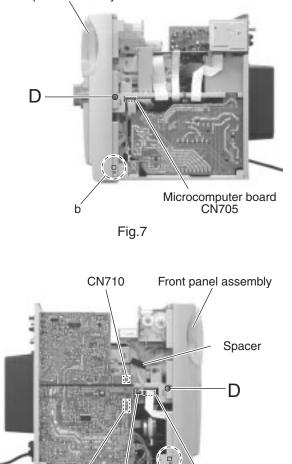

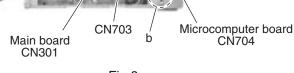

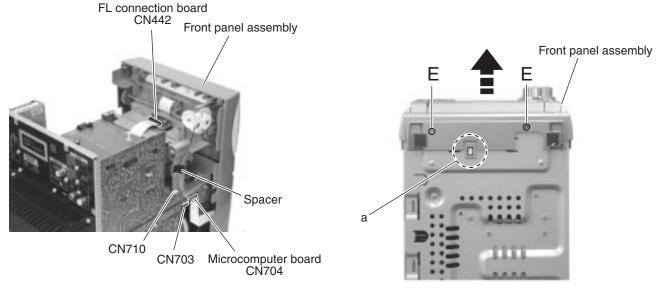

#### Removing the front panel assembly (See Fig.7~10)

- Prior to performing the following procedure, remove the metal cover and the DVD mechanism assembly.

- 1. Disconnect the card wire from connector CN705 on the microcomputer board in the center of the right side of the body.

- 2. Disconnect the card wire from connector CN301 on the main board in the center of the left side of the body.

- 3. Disconnect the card wire from connector CN704, and the wires from CN703 and CN710 on the microcomputer board.

ATTENTION: When disconnecting the wires from CN703 and CN710, remove the spacer attaching the wires.

- 4. Disconnect the card wire from connector CN442 on the FL connection board on top of the body.

- 5. Remove the screw **D** on each side of the body.

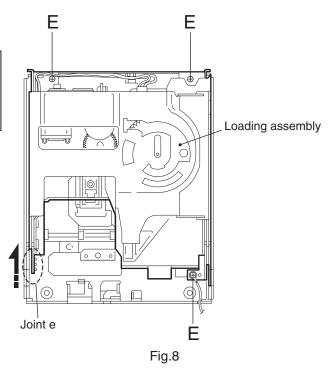

- 6. Remove the two screws **E** on the bottom of the body.

- 7. Release the joint **a** on the bottom and the two joints **b** on the right and left sides of the body using a screwdriver. Remove the front panel assembly toward the front.

Front panel assembly

Fig.9

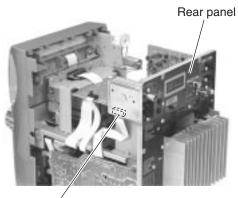

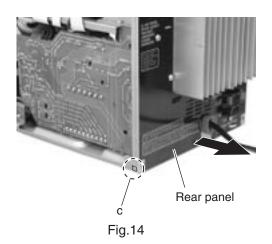

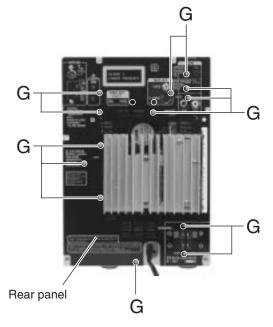

#### ■ Removing the rear cover/ rear panel (See Fig.11~15)

- Prior to performing the following procedure, remove the metal cover and the DVD mechanism assembly.

- 1. Remove the two screws **F** on the back of the body.

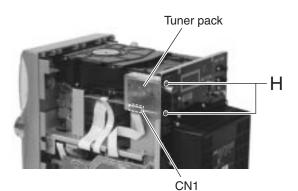

- 2. Disconnect the wire from connector CN1 on the tuner pack on the right side of the body.

- 3. Remove the thirteen screws **G** on the back of the body.

- 4. Release the two joints **c** on the lower right and left sides of the rear panel.

REFERENCE: The rear panel with the tuner pack comes off.

Rear cover

Tuner pack CN1

#### UX-A10DVD

#### ■ Removing the tuner pack (See Fig.16)

- Prior to performing the following procedure, remove the metal cover.

- 1. Disconnect the card wire from connector CN1 on the tuner pack on the right side of the body.

- 2. Remove the two screws **H** on the back of the body.

Fig.16

#### Removing the fan

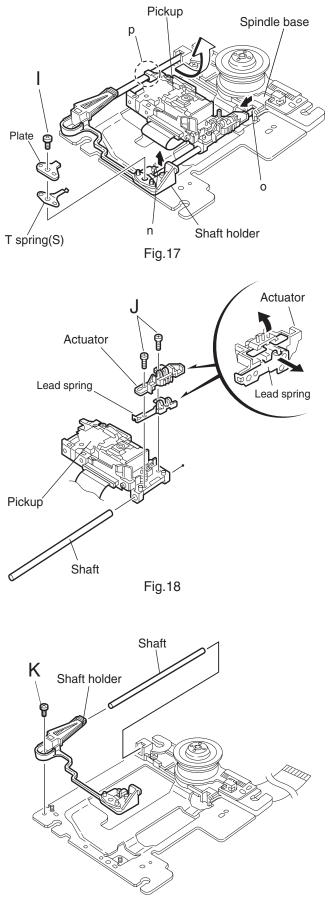

#### (See Fig.17,18)

- Prior to performing the following procedure, remove the metal cover, the DVD mechanism assembly, the rear cover/rear panel and the DVD relay board.

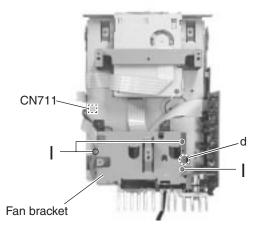

- 1. Disconnect the wire from connector CN711 on the microcomputer board on the right side of the body.

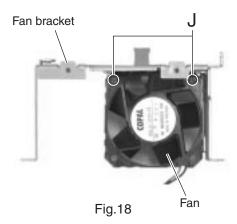

- 2. Remove the three screws I attaching the fan bracket on top of the body and release the joint **d**.

- 3. Remove the two screws **J** attaching the fan.

Fig.17

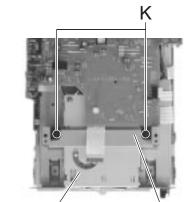

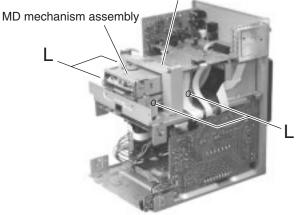

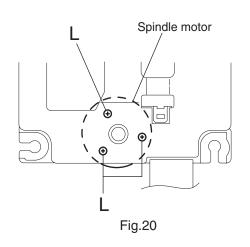

#### Removing the MD mechanism assembly (See Fig.19~21)

- · Prior to performing the following procedure, remove the metal cover, the DVD mechanism assembly and the front panel assembly.

- 1. Remove the two screws K attaching the DVD mechanism attaching bracket.

- 2. Remove the two screws L on each side of the MD mechanism assembly and remove the MD mechanism assembly toward the front.

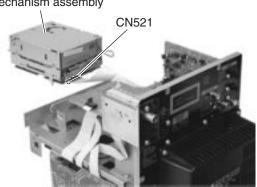

- 3. Disconnect the card wire from connector CN521 on the MD mechanism assembly board.

Fig.19

MD mechanism assembly

**DVD** mechanism attaching bracket

DVD mechanism attaching bracket

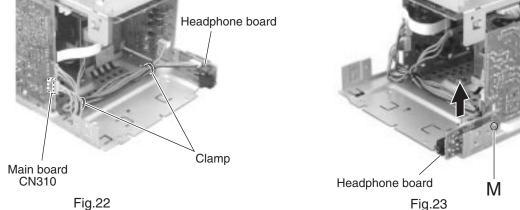

#### Removing the headphone board (See Fig.22,23)

- · Prior to performing the following procedure, remove the metal cover, the DVD mechanism assembly and the front panel assembly.

- 1. Disconnect the wire from connector CN310 on the main board on the left side of the body.

- 2. Release the wires from the two clamps on the bottom chassis.

- 3. Remove the screw M attaching the headphone board on the right side of the body.

Fig.20 MD mechanism assembly

Fig.21

Fig.22

#### UX-A10DVD

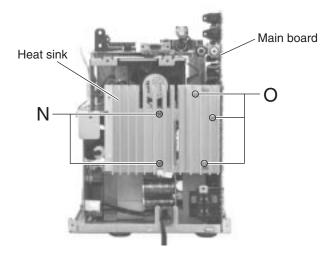

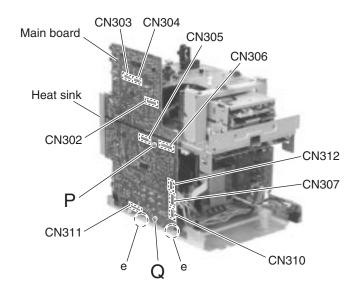

#### ■ Removing the main board

(See Fig.24,25)

- Prior to performing the following procedure, remove the metal cover, the DVD mechanism assembly, the front panel assembly and the rear cover/ rear panel.

- 1. Remove the two screws  $\,N$  and the three screws  $\,O.\,$  Remove the heat sink.

- Disconnect the wires from connector CN307 and CN310, the card wire from CN312 on the main board on the left side of the body.

- 3. Remove the screw **P** and **Q** attaching the main board.

- Disconnect connector CN303, CN304, CN305 and CN306 on the main board. Release the two joints e at the bottom.

- 5. Draw out the main board and disconnect the card wire and the wire from connector CN302 and CN311.

Fig.26

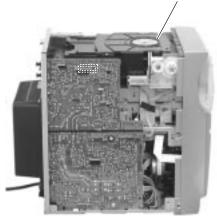

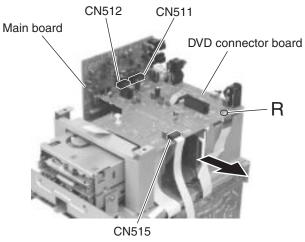

#### Removing the DVD relay board (See Fig.26)

- Prior to performing the following procedure, remove the metal cover, the DVD mechanism assembly and the rear panel/ rear cover.

- 1. Disconnect the card wire from connector CN515 on the DVD relay board.

- 2. Remove the screw **R** attaching the DVD relay board on top of the body.

- 3. Disconnect connector CN511 and CN512 on the DVD relay board.

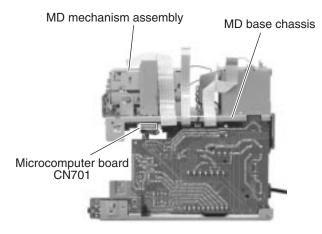

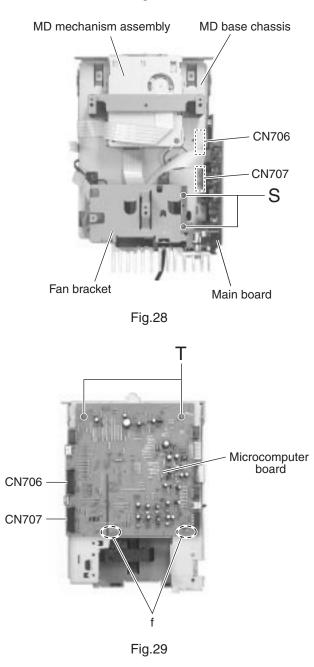

#### Removing the MD base chassis/ microcomputer board (See Fig.27~29)

• Prior to performing the following procedure, remove the metal cover, the DVD mechanism assembly, the front panel assembly, the rear cover/ rear panel, the main board and the DVD relay board.

REFERENCE: It is not necessary to remove the DVD mechanism assembly.

- 1. Disconnect the wire from connector CN701 on the microcomputer board in the center of the right side of the body.

- 2. Remove the two screws **S** attaching the MD base chassis on top of the body.

- 3. Disconnect connector CN706 and CN707 on the microcomputer board from the main board.

REFERENCE: The MD base chassis with the MD mechanism assembly comes off.

4. Remove the two screws **T** attaching the microcomputer board and release the two joints **f**.

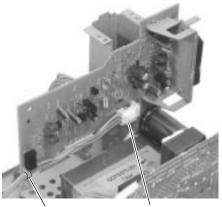

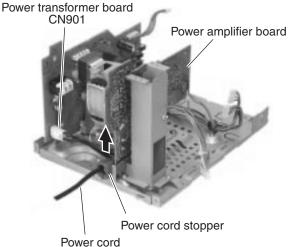

# Removing the power transformer assembly (See Fig.30,31)

- Prior to performing the following procedure, remove the metal cover, the DVD mechanism assembly, the front panel assembly, the rear cover/ rear panel, the main board and the MD base chassis.

- 1. Move the power cord stopper upward on the back of the body and remove. Disconnect the power cord from connector CN901 on the power transformer board.

REFERENCE: The power cord can be removed alone.

2. Remove the four screws **U** on top of the body and release the wires from the two clamps on the bottom chassis.

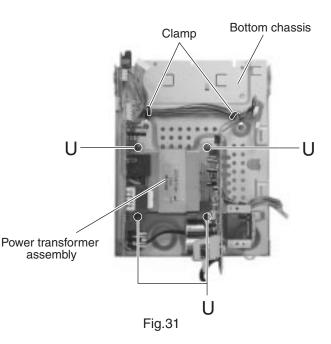

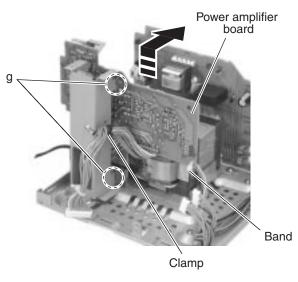

#### Removing the power amplifier board (See Fig.32,33)

- Prior to performing the following procedure, remove the metal cover, the DVD mechanism assembly, the front panel assembly, the rear cover/ rear panel, the main board and the MD base chassis.

- 1. Disconnect the wire from connector CN111 on the power amplifier board.

- 2. Remove the band attaching the wire to the power amplifier board.

- 3. Release the wires from the clamp.

- 4. Move the power amplifier board upward to release the two joints **g** and remove to the right.

Band Power amplifier board CN111

Fig.32

er cord

Fig.30

Fig.33

#### <Front panel assembly>

• Prior to performing the following procedure, remove the metal cover, the DVD mechanism assembly and the front panel assembly.

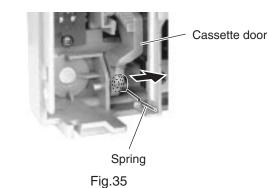

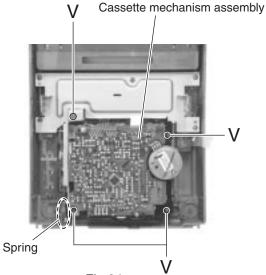

# ■Removing the cassette mechanism assembly (See Fig.34,35)

- 1. Remove the spring attached to the cassette door on the back of the front panel.

- 2. Remove the four screws **V** attaching the cassette mechanism assembly.

Fig.34

Fig.36

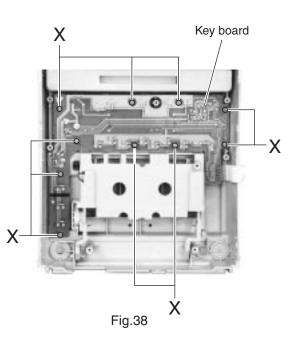

#### ■ Removing the key board (See Fig.36~38)

- Prior to performing the following procedure, remove the cassette mechanism assembly.

- 1. Pull out the volume knob on the front side of the front panel.

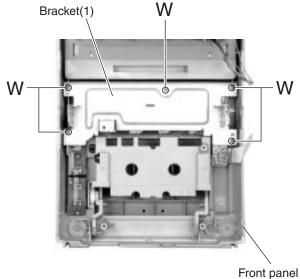

- 2. Remove the five screws W attaching the bracket (1) on the back of the front panel.

- 3. Remove the ten screws **X** attaching the key board.

Fig.37

#### UX-A10DVD

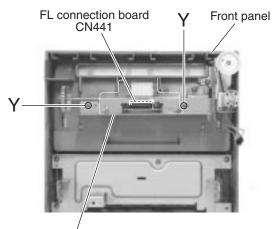

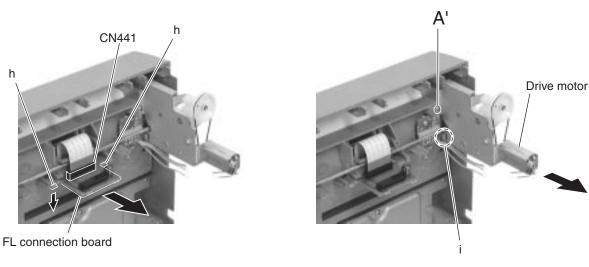

#### Removing the FL connection board (See Fig.39~41)

- 1. Remove the two screws **Y** and the screw **Z** attaching the bracket (2) on the back of the front panel.

- 2. Disconnect the card wire from connector CN441 on the FL connection board.

- 3. Push the two joint tabs **h** downward to release and pull out the FL connection board.

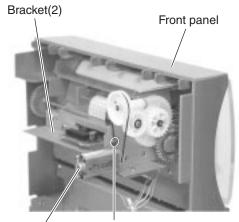

#### ■ Removing the Drive motor assembly (See Fig.39, 40,42)

- 1. Remove the two screws **Y** and the screw **Z** attaching the bracket (2) on the back of the front panel.

- 2. Remove the screw **A'** attaching the drive motor assembly. Release the joint tab **i** and pull out the drive motor assembly.

Fig.40

Ζ

Fig.41

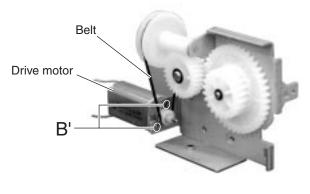

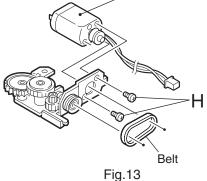

# ■ Removing the belt/ drive motor

(See Fig.43)

- Prior to performing the following procedure, remove the drive motor assembly.

- 1. Remove the belt from the pulley

- 2. Remove the two screws **B'** attaching the drive motor.

Fig.43

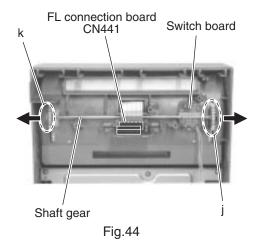

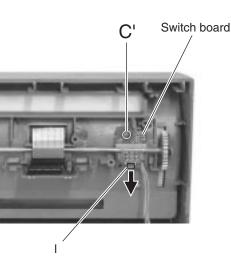

#### Removing the switch board (See Fig.44,45)

- Prior to performing the following procedure, remove the bracket (2) / drive motor assembly.

- 1. Disconnect the card wire from connector CN441 on the FL connection board(Do not fold down the card wire).

- 2. Release the joint **j** and **k** in order on the right and left sides of the shaft gear.

Remove the screw **C**' attaching the switch board and release the joint tab **I**.

Fig.45

#### UX-A10DVD

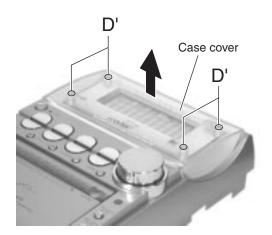

#### ■ Removing the FL display section (See Fig.46~51)

- 1. Remove the four screws **D'** attaching the case cover on the front panel.

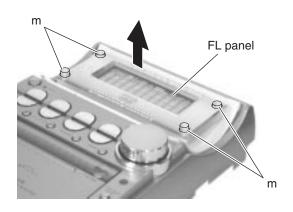

- 2. Pull out the FL panel from the four joint bosses **m** on the FL display cover.

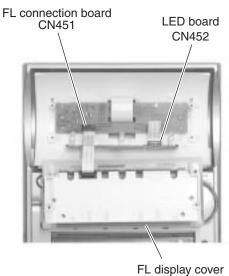

- 3. Remove the four screws **E'** attaching the FL display cover. Disconnect the card wire from connector CN451 on the FL relay board and from CN452 on the LED board.

Fig.47

Fig.48

FL display cov Fig.49

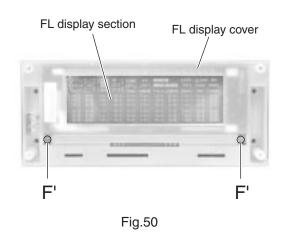

- 4. Remove the two screws **F'** attaching the FL display on the FL display cover.

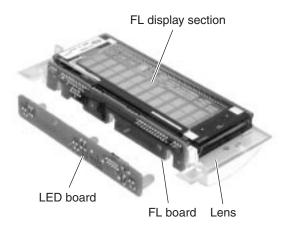

- 5. The FL board and the lens come off from the FL display section.

Fig.51

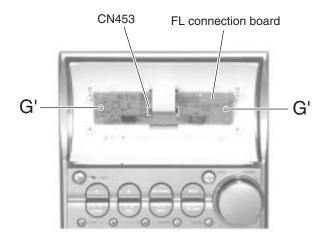

#### ■ Removing the FL relay board(See Fig.52)

- Prior to performing the following procedure, remove the FL display cover.

- 1. Disconnect the card wire from connector CN453 on the FL relay board.

- 2. Remove the two screws **G'** attaching the FL relay board.

Fig.52

#### <DVD loading mechanism section>

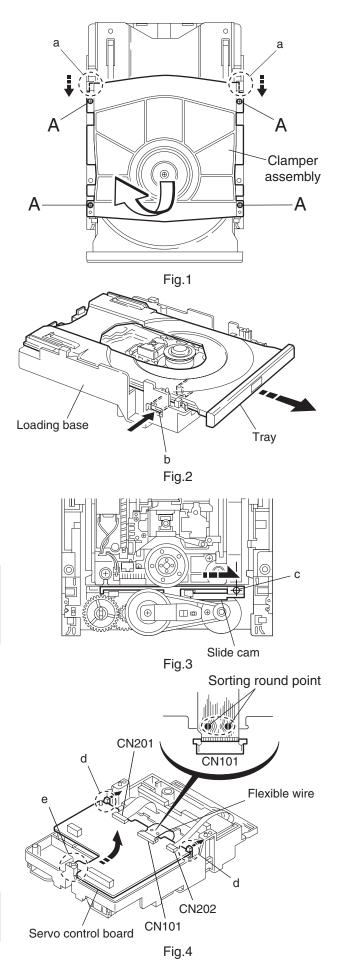

#### ■Removing the clamper assembly

(See Fig.1)

- 1. Remove the four screws **A** attaching the clamper assembly.

- 2. Move the clamper assembly in the direction of the arrow to release the joint **a** on each side, and remove.

ATTENTION: When reassembling, reattach the clamper assembly at the two joints **a**.

#### ■Removing the tray (See Fig.2,3)

- Prior to performing the following procedure, remove the clamper assembly.

- 1. Push the part b of the slide cam through the slot on the left side of the loading base.

- 2. Draw out the tray toward the front.

ATTENTION: When reattaching the tray, move the part c of the slide cam to the right(See Fig.3).

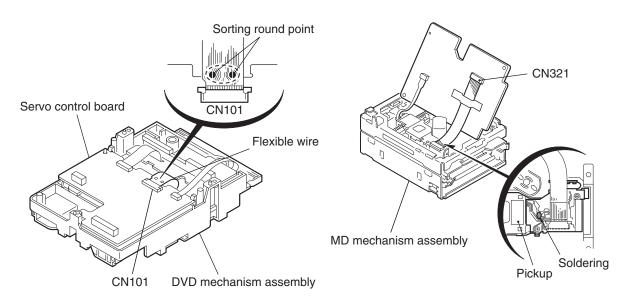

#### Removing the servo control board (See Fig.4)

CAUTION: Solder the sorting round point before disconnecting the flexible wire extending from the pickup. If you do not follow this instruction, the pickup may be damaged.

- 1. Solder the sorting round point on the flexible wire connected to connector CN101 on the servo control board.

- 2. Disconnect the flexible wire from connector CN101 on the servo control board.

- 3. Disconnect the card wires from connector CN201 and CN202 on the servo control board.

- 4. Release the two joints d.

- 5. Move the servo control board in the direction of the arrow to release the joint e, and remove upward.

CAUTION: Unsolder the sorting round point after reassembling.

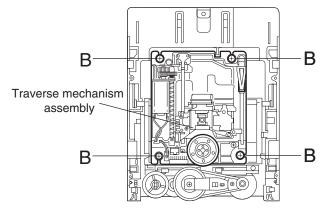

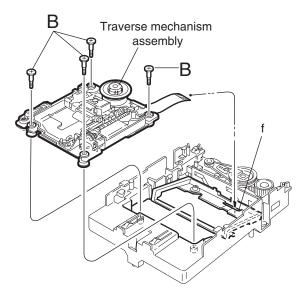

#### Removing the traverse mechanism assembly (See Fig.5,6)

- Prior to performing the following procedure, remove the clamper assembly, the tray and the servo control board.

- 1. Remove the four screws **B** attaching the traverse mechanism assembly.

CAUTION: When reassembling, get the flexible wire extending from the spindle motor board through the slot f of the elevator.

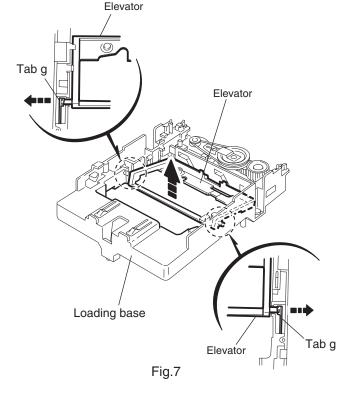

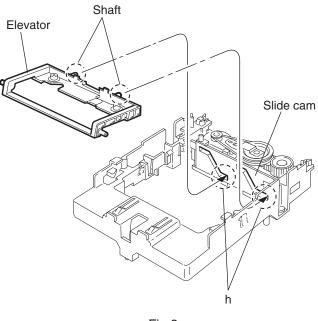

#### Removing the elevator (See Fig.7 and 8)

- Prior to performing the following procedure, remove the clamper assembly, the tray, the servo control board and the traverse mechanism assembly.

- 1. Pull the two tabs **g** outward and release the two shafts of the elevator.

ATTENTION: When reassembling, fit the two shafts on the front side of the elevator into the grooves h of the slide cam.

Fig.8

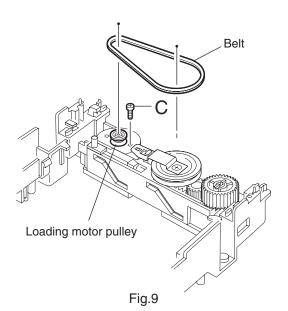

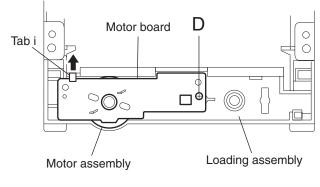

#### ■Removing the motor assembly

(See Fig.9,10)

- Prior to performing the following procedure, remove the clamper assembly, the tray, the servo control board, the traverse mechanism assembly and the elevator.

- 1. Remove the belt from the pulley.

- 2. Remove the screw **C** attaching the loading motor.

- 3. Remove the screw **D** attaching the motor board on the back of the loading assembly.

- 4. Release the tab i fixing the motor board and remove the motor assembly.

Fig.10

$\cap$

Slide cam

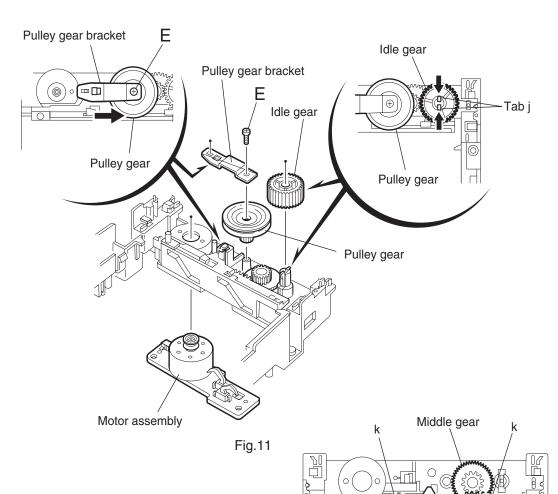

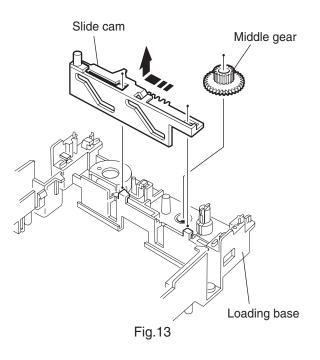

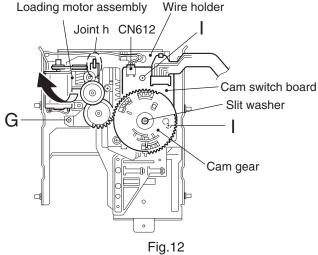

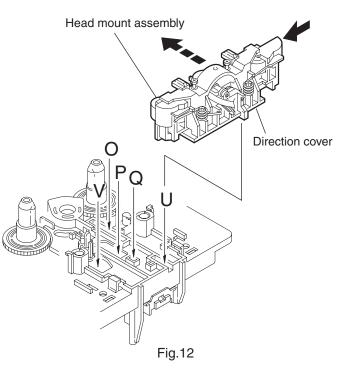

#### Removing the idle gear/ pulley gear/ middle gear/ slide cam (See Fig.11~13)

- Prior to performing the following the procedures, remove the clamper assembly, the tray, the servo control board, the traverse mechanism assembly, the elevator and the motor assembly.

- 1. Push the two tabs j attaching the idle gear inward and pull out the idle gear.

- 2. Remove the screw E attaching the pulley gear bracket. Move the pulley gear bracket in the direction of the arrow and remove upward.

- 3. Pull out the pulley gear.

- 4. Move the slide cam in the direction of the arrow to release the two joints k and remove upward.

- 5. Remove the middle gear.

Fig.12

### <DVD traverse mechanism assembly>

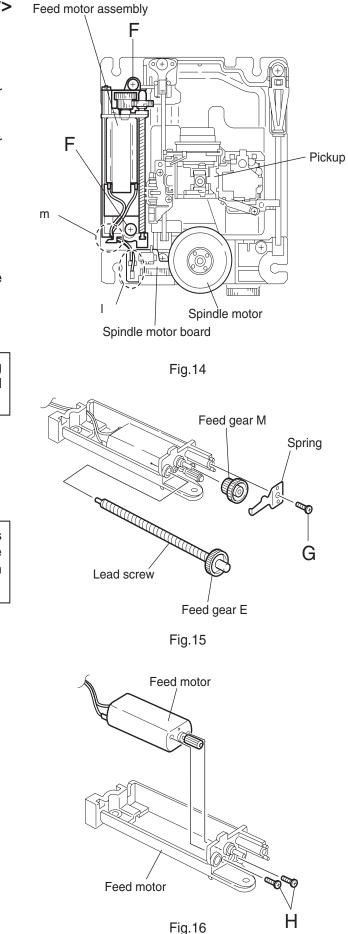

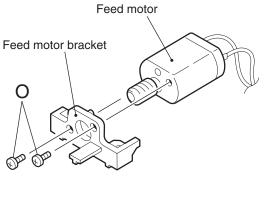

#### ■Removing the feed motor assembly (See Fig.14)

- 1. Unsolder the two soldering I on the spindle motor board.

- 2. Remove the two screws **F** attaching the feed motor assembly.

#### Removing the feed motor

(See Fig.14~16)

- Prior to performing the following procedure, remove the feed motor assembly.

- 1. Remove the screw **G** and the spring.

CAUTION: When reassembling, attach the spring correctly to press the feed gear M and E.

- 2. Remove the feed gear M.

- 3. Pull out the feed gear E and the lead screw.

- 4. Remove the two screws **H** and the feed motor.

CAUTION: When reassembling, set the two wires extending from the feed motor to the notch **m** of the feed holder as shown in Fig.14.

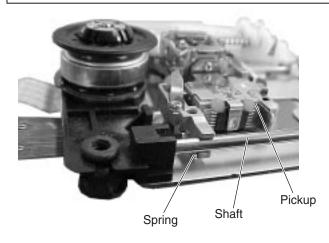

#### Removing the pickup (See Fig.17,18)

- 1. Prior to performing the following procedure, remove the feed motor assembly.

- 2. Remove the screw I, the T spring(S) and the shaft holder with the plate.

ATTENTION: When reassembling, reattach the T spring (s) correctly to press the shaft

- 3. Detach the part **n** of the shaft upward and move the part **o** in the direction of the arrow, then remove the shaft from the spindle base.

- 4. Release the joint **p** in the direction of the arrow.

Pull out the shaft from the pickup.

- 5. Remove the two screws  $\mathbf{J}$  attaching the actuator.

- 6. Release the joint of the actuator and the lead spring, and pull out the lead spring.

ATTENTION: When reattaching the pickup, attach the spring under the shaft(See the figure below).

#### Removing the shaft holder/ shaft (SeeFig.19)

- Prior to performing the following procedure, remove the feed motor assembly and the pickup.

- 1. Remove the screw  $\,\,\textbf{K}$  attaching the shaft holder.

- 2. Remove the shaft.

Fig.19

#### ■ Removing the spindle motor assembly (See Fig.20~22)

- Prior to performing the following procedure, remove the feed motor assembly, the pickup, the shaft and the shaft holder.

- 1. Turn over the mechanism base and remove the three screws I attaching the spindle motor assembly.

ATTENTION: When reassembling, set the card wire extending from the spindle motor board to the notch of the spindle base.

2. Remove the three screws **M** and the spindle base.

Spindle motor assembly 、

Fig.22

#### <MD mechanism assembly>

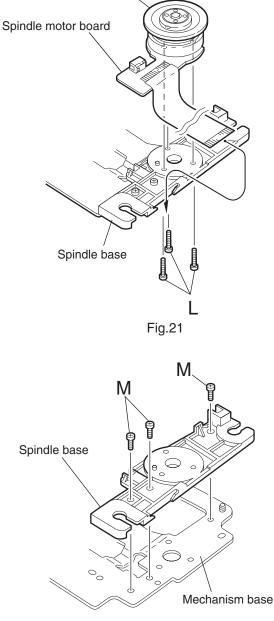

#### Removing the main board (See Fig.1, 2)

CAUTION: When replacing the flexible wire connected to the main board, solder the shorting round point. Otherwise, the pickup may be damaged. (see Fig.18)

- 1. Turn over the main body and disconnect the card wire from connector CN408 and the flexible wire from CN407 on the main board respectively.

- 2. Remove the two screws **A** attaching the main board. Move the main board in the direction of the arrow to release the two joints  $\mathbf{a}$ .

- 3. Solder the sorting round point to protect the pickup. Disconnect the flexible wire from connector CN321 on the back of the main board.

CAUTION: When reassembling, connect the flexible wire from the pickup to the main board and unsolder the shorting round point.

- 1. Remove the four screws  ${\bf B}\,$  on each side of the body.

- 2. Remove the one screw **C** on the upper side of the body.

- 3. Move the mechanism cover toward the front to release the front hook from the loading assembly (joint  ${\bf b}$ ) , then remove upward.

#### UX-A10DVD

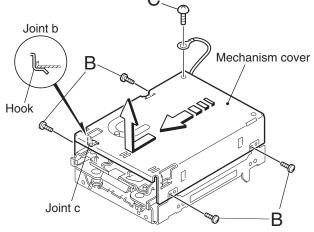

#### Removing the head lifter (See Fig.4~6)

- 1. Removing the spring from the hook on the main body. Remove the spring from the head lifter if necessary.

- 2. Turn the head lifter in the direction of the arrow to release the joint **c** and **d**.

Head lifter

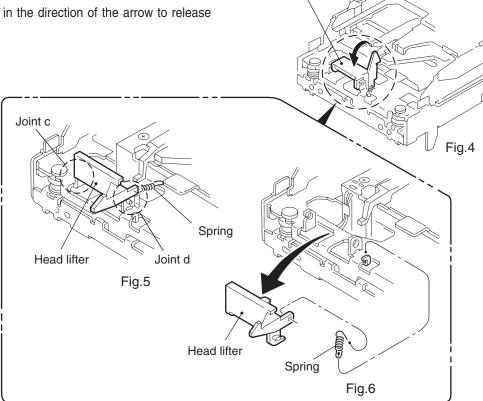

#### Removing the head assembly (See Fig.7)

- · Prior to performing the following procedure, remove the main board.

- 1. Remove the screw **D** on the upper side of the body. Remove the head assembly while pulling the flexible harness from the body.

#### Removing the loading assembly (See Fig.8, 9)

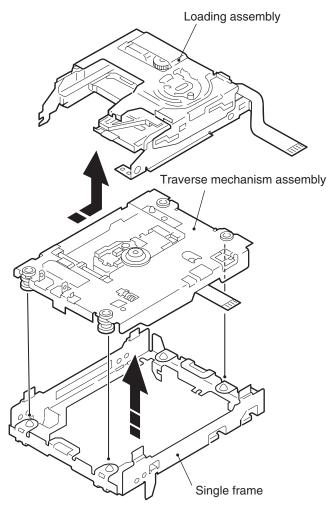

REFERENCE: The traverse mechanism assembly and the single flame can be removed after removing the loading assembly from the body.

- Prior to performing the following procedure, remove the main board, the mechanism cover and the head lifter/head assembly.

- 1. Remove the three screws **E** on the upper side of the body.

- 2. Move the loading assembly toward the front to release the joint **e** and remove upward.

- 3. Remove the traverse mechanism assembly from the single flame.

Fig.9

side.

#### <Loading assembly section>

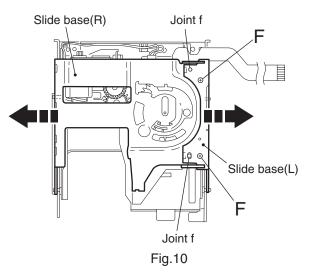

#### Removing the slide base (L) and (R) (See Fig.10)

- 1. Remove the two screws **F** on the upper side of the loading base assembly.

- 2. Remove the slide base (L) outward while releasing the two joints  ${\bf f}$  on the bottom.

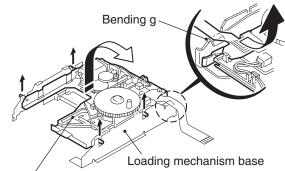

Removing the loading mechanism assembly

To release the loading mechanism assembly from the bending g without trouble, first bring up the one side of the loading mechanism assembly opposite to the bending g and release the side bosses from the loading mechanism base. And next, remove another

3. Remove the slide base (R) outward.

Loading mechanism assembly

#### - Loading mechanism assembly section -

#### Removing the loading motor

(See Fig.12, 13)

(See Fig.11)

- 1. Release the harness from the wire holder on the cam switch board and disconnect from connector t.

- 2. Remove the screw  ${\bm G}\,$  and release the joint  $\,{\bm h}\,.$

- 3. Remove the belt from the loading motor assembly.

- 4. Remove the two screws H.

#### Remove the cam gear and the cam switch board (See Fig.12)

- 1. Remove the slit washer and pull out the cam gear.

- 2. Release the harness from the wire holder on the cam switch board and disconnect from connector CN612.

- 3. Remove the two screws  ${\rm I}\,$  , the clamp and the cam switch board.

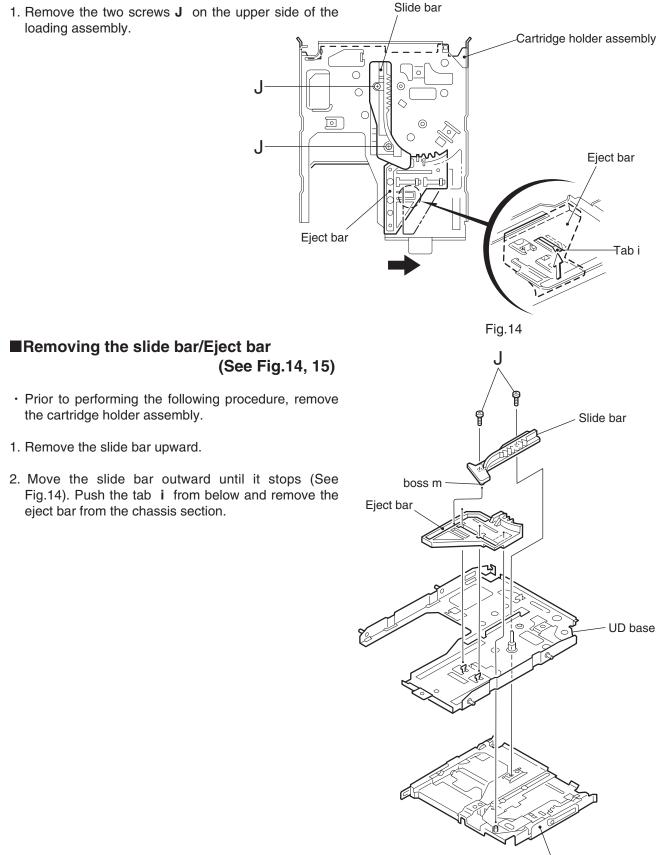

# Remove the cartridge holder assembly (See Fig.14, 15)

Cartridge holder assembly

1-30

#### UX-A10DVD

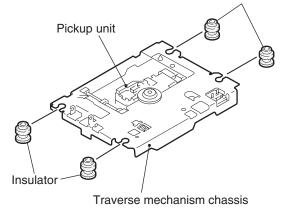

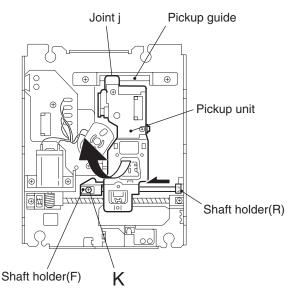

### <Traverse mechanism assembly section>

(See Fig.16)

(See Fig.17)

#### Removing the insulator

Removing the pickup unit

1. Removing the insulators from the four notches of the traverse mechanism chassis.

Insulator

Fig.16

- 1. Remove the screw **K** attaching the shaft holder (F) on the back of the traverse mechanism assembly.

- 2. Move the shaft inward and release from the shaft holder (R).

- 3. Bring up the one side of the pickup unit on the shaft to release the joint **j** on the opposite side. Then, remove the pickup unit with the shaft.

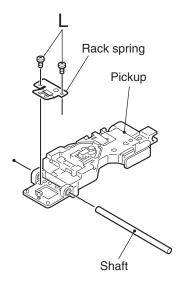

#### Removing the pickup

(See Fig.18)

- 1. Pull out the shaft from the pickup.

- 2. Remove the two screws L attaching the rack spring to the pickup.

CAUTION: Before disconnecting the flexible wire connected to the pickup, solder the shorting round point to protect the pickup from static electricity.

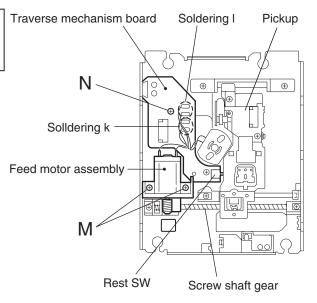

#### Removing the feed motor assembly (See Fig.19,20)

REFERENCE: The feed motor assembly can be performed even if the pickup unit is attached.

- For the white and black harnesses extending from the feed motor assembly, unsolder two soldering k on the traverse mechanism board.

- 2. Remove the two screws  ${\rm M}\,$  attaching the feed motor assembly.

- Remove the two screws O attaching the feed motor bracket.

- Prior to performing the following procedure, remove the feed motor assembly.

- 1. For the red and black harnesses extending from the spindle motor, unsolder two soldering I on the traverse mechanism board.

- 2. Remove the screw  ${\bf N}$  .

CAUTION: When reattaching the traverse mechanism board, make sure the position of the pickup. If the pickup is on the most inside position, move it outward by turning the screw shaft gear not to contact with the rest SW.

Fig.19

### <Reattaching the loading assembly section>

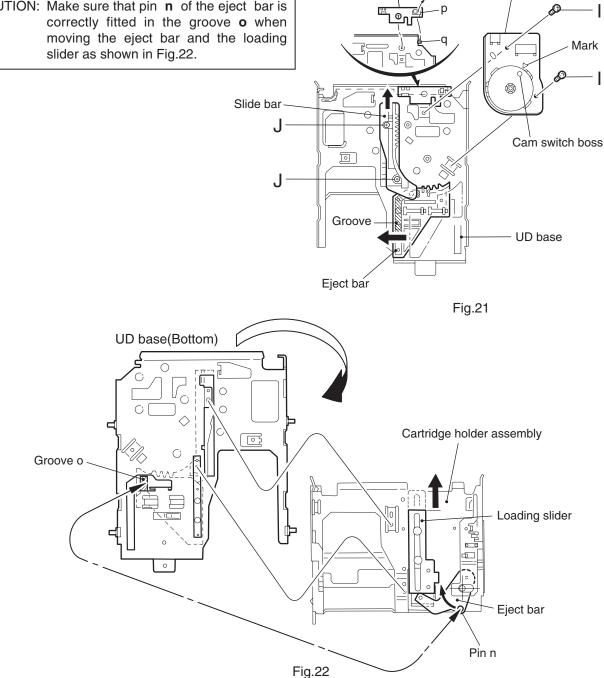

- 1. Reattach the eject bar to the UD base (see Fig.15, 21).

- 2. Reattach the slide bar to the loading mechanism chassis while fitting the boss **m** to the groove of the eject bar (see Fig.15).

- 3. Move the slide bar and eject bar in the direction of the arrow and reattach the cartridge holder assembly using the two screw J (Fig.21, 22).

CAUTION: Make sure that pin **n** of the eject bar is moving the eject bar and the loading

Wire holder

Cam switch board

- 4. Reattach the wire holder to the UD base while fitting the bending **q** to the hole of the wire holder (The boss on the back of the wire holder is fit to the hole of the UD base)(see Fig.21).

- 5. Reattach the cam switch board using the two screws  ${\rm I}$  .

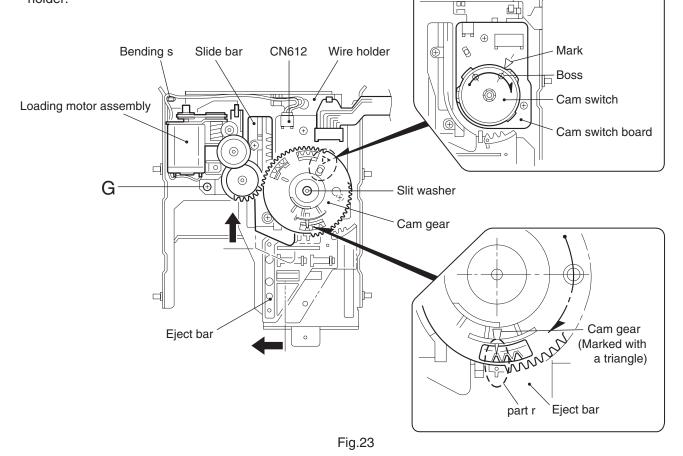

- Turn the cam switch until the boss comes to the position marked with a triangle (see Fig.23). Reattach the cam gear while fitting the cam gear slot to the cam switch boss, and fix them using the slit washer.

CAUTION: When reattaching the cam gear with fitting the slot to the cam switch boss, make sure that part **r** of the gear is aligned with the position marked with a triangle of the cam gear.

7. Reattach the loading motor assembly using the screw **G** (see Fig.23).

Connect the wire extending from the loading motor to connector CN612 on the switch board, set on the bending  $\mathbf{s}$  of the UD base and fix using the wire holder.

#### UX-A10DVD

8. Reattach the UD base to the loading mechanism base while fitting the four bosses to the notches of the loading mechanism base respectively (see Fig.24).

First, sit part t of the cartridge holder assembly under the bending g of the loading mechanism base, then reattach the UD base.

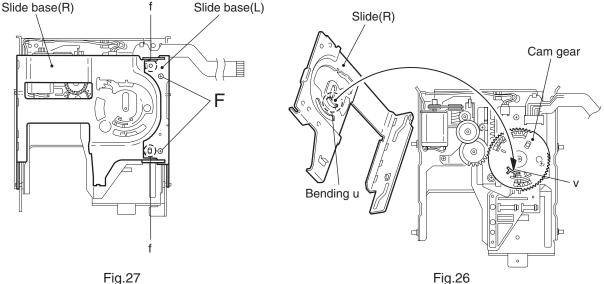

9. Reattach the slide base (R) while fitting the two slots of the slide base (R) to the bosses of the UD base (see Fig.25, 26).

CAUTION: Set the bending **u** of the slide base (R) to the part  $\mathbf{v}$  inside of the cam gear rib.

10. Reattach the slide base (L) on the slide base (R) while fitting the two bosses of the UD base to the notches on the side of the slide base (L). Make sure that the slots of the slide base (L) are fitted to the two part f and fix the slide base (L) using the two screws **F** (see Fig.25, 27).

REFERENCE: To reattach the slide base (L) and (R) easily, fit the bosses to the notches with bringing up the UD base slightly.

Pin Pin Loading mechanism base Fig.24 Slide base(R) Bending u Pin Slide base(L) Pin

Fig.25

Fig.27

#### <Cassette mechanism assembly section>

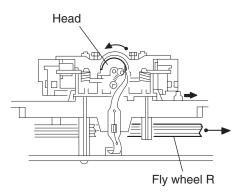

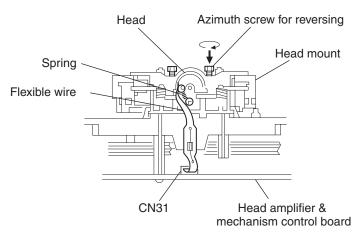

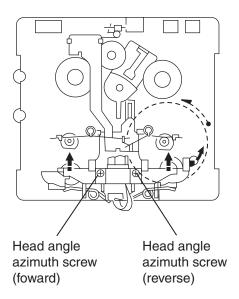

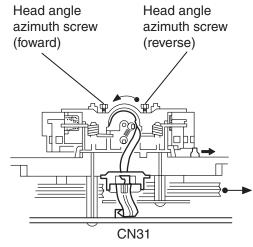

#### ■ Removing the Play/Record & Clear head (See Fig.1~3)

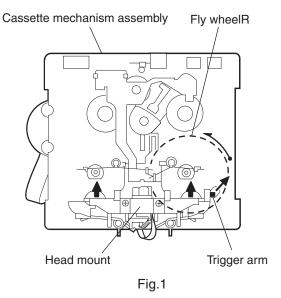

- 1. While moving the trigger arm on the right side of the head mount in the direction of the arrow, turn the flywheel R counterclockwise until the head mount comes ahead and clicks.

- 2. The head turns counterclockwise as you turn the flywheel R counterclockwise(See Fig.2 and 3).

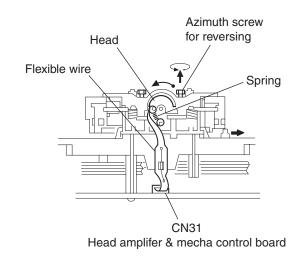

- 3. Disconnect the flexible wire from connector CN31 on the head amplifier & mecha control board.

- 4. Remove the spring from the back of the head.

- 5. Loosen the azimuth screw for reversing attaching the head.

- 6. Remove the head on the front side of the head mount.

#### UX-A10DVD

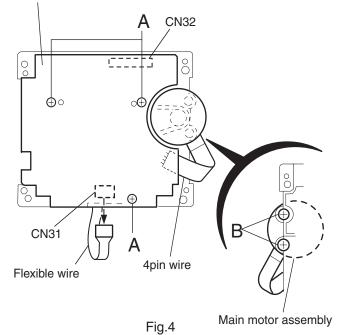

#### Removing the head amplifier & mechanism control board (See Fig.4)

- 1. Turn over the cassette mechanism assembly and remove the three screws **A** attaching the head amplifier & mechanism control board.

- 2. Disconnect the flexible wire from connector CN31 on the head amplifier & mechanism control board.

- 3. Disconnect connector CN32 of the head amplifier & mechanism control board from connector CN1 on the reel pulse board.

REFERENCE: If necessary, unsolder the 4 pin wire soldered to the main motor.

Head amplifier & mecha control board

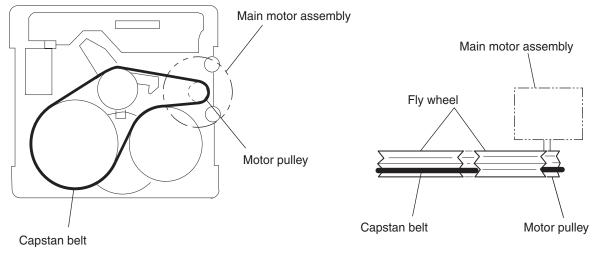

#### ■ Removing the main motor (See Fig.4~7)

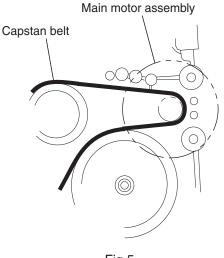

- 1. Remove the two screws  $\, {\bf B}$  .

- 2. Half raise the motor and remove the capstan belt from the motor pulley.

ATTENTION: Be careful to keep the capstan belt from grease. When reassembling, refer to Fig.6 and 7 for attaching the capstan belt.

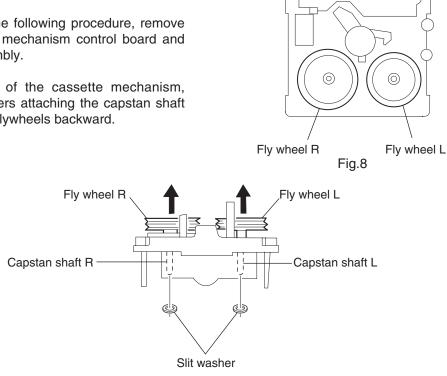

#### Removing the flywheel (See Fig.8,9)

- · Prior to performing the following procedure, remove the head amplifier & mechanism control board and the main motor assembly.

- 1. From the front side of the cassette mechanism, remove the slit washers attaching the capstan shaft L and R. Pull out the flywheels backward.

Fig.9

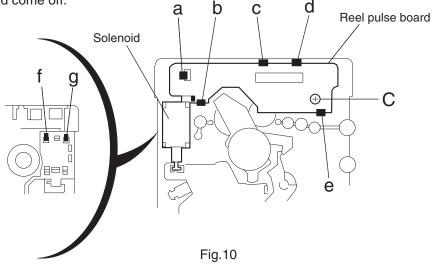

#### Removing the reel pulse board and solenoid (See Fig.10)

- · Prior to performing the following procedure, remove the head amplifier & mechanism control board.

- 1. Remove the screw C.

- 2. Release the tab a, b, c, d and e retaining the reel pulse board.

- 3. Release the tab f and g attaching the solenoid on the reel pulse board.

- 4. The reel pulse board and the solenoid come off.

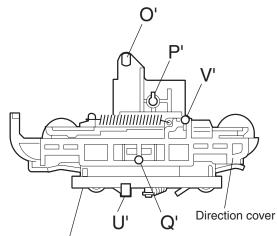

# Reattaching the Play/ Record & Clear head (See Fig.11~13)

- 1. Reattaching the head mount assembly.

- 1) Change front of the direction cover of the head mount assembly to the left(Turn the head forward).

- Fit the bosses O',P',Q',U' and V' on the head mount assembly to the holes P and V, the slots O,U and Q of the mecha sub assembly(See Fig.11 to 13).

- CAUTION: To remove the head mount assembly, turn the direction cover to the left to disengage the gear. If the gear can not be disengaged easily, push up the boss **Q'** slightly and raise the rear side of the head mounts slightly to return the direction lever to the reversing side.

- 2. Tighten the azimuth screw for reversing.

- 3. Reattach the spring from the back of the Play/ Record & Clear head.

- 4. Connect the flexible wire to connector CN31 on the head amplifier & mechanism control board.

Head mount assembly

Fig.11

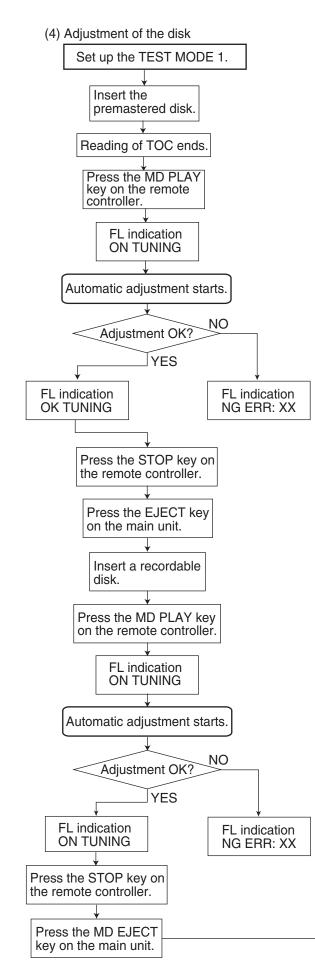

# Adjustment method < MD adjustment (self adjustment) >

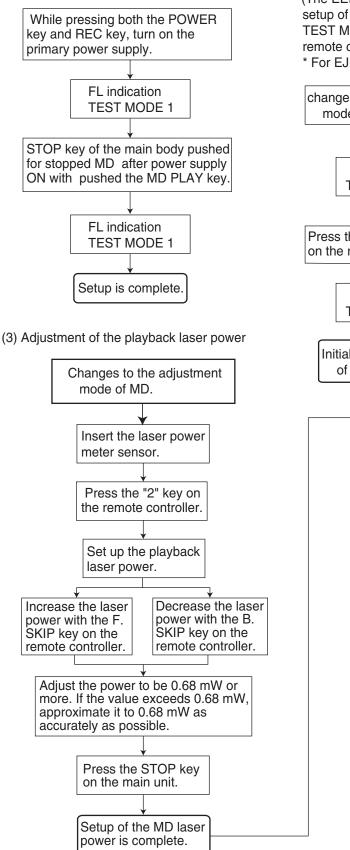

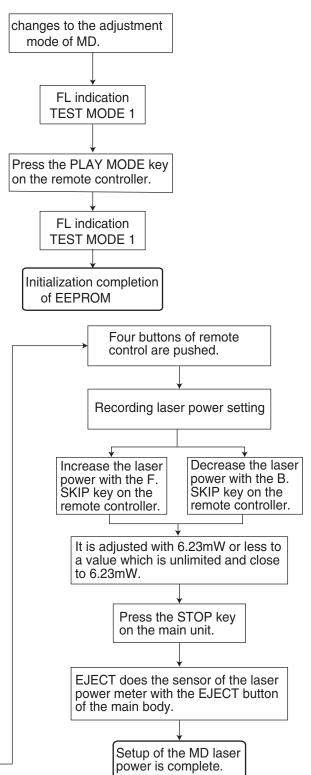

(1) Setting of adjustment mode of MD

(2) Initialization of EEPROM

(The EEPROM can be initialized on the precondition that the setup of the TEST MODE 1 is complete. After setup of the TEST MODE 1, proceed to the following operations with the remote controller\*.)

\* For EJECT operation, use the EJECT key on the main unit.

|      | NG Judgment Code Table                            |  |  |  |  |

|------|---------------------------------------------------|--|--|--|--|

| Code | NG item in adjustment                             |  |  |  |  |

| 00   | Automatic adjustment is incomplete.               |  |  |  |  |

| 01   | Rest switch detection                             |  |  |  |  |

| 02   | Focus-on                                          |  |  |  |  |

| 03   | EF balance, tracking offset adjustment (Pit area) |  |  |  |  |

| 04   | ABCD level (I-V resistance) adjustment (Pit area) |  |  |  |  |

| 05   | Focus servo AGC (Pit area)                        |  |  |  |  |

| 06   | Tracking servo AGC (Pit area)                     |  |  |  |  |

| 07   | Focus bias adjustment (Pit area)                  |  |  |  |  |

| 08   | EF balance, tracking offset adjustment (GRV area) |  |  |  |  |

| 09   | ABCD level (I-V resistance) adjustment (GRV area) |  |  |  |  |

| 0A   | Focus servo AGC (GRV area)                        |  |  |  |  |

| 0B   | Tracking servo AGC (GRV area)                     |  |  |  |  |

| 0C   | Focus bias adjustment (GRV area)                  |  |  |  |  |

| 0D   | Room temperature measurement                      |  |  |  |  |

| 0E   | Write in EEPROM                                   |  |  |  |  |

| FF   | Automatic adjustment is complete.                 |  |  |  |  |

# <Method of setting DVD test mode>

- 1.Main body "Stop button " and "DVD eject button ▲ " are pushed at the same time, and the power supply is turned on.

- 2. The display of the FL display becomes "TEST D", and becomes a test mode.

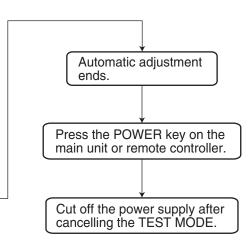

| Т | E | S | Т |  | D | R | 2 |

|---|---|---|---|--|---|---|---|

|   |   |   |   |  |   |   |   |

3.Comes off the test mode when the power supply is turned off by "STANDBY button  $\oplus$ /I ".

4.Use key in test mode

[STOP]+[DVD EJECT]+AC opening:Test mode [STANDBY]:Test mode release

[ON SCREEN] : Self adjustment command for test

[DVD EJECT] : EJECT command for test

[STOP] : STOP command for test

[DVD PAUSE] : Self adjustment command for test

[DVD PLAY] : Jitter measurement command for test

[ENTER] : EEPROM initialization command

[▶▶I] : Outer tracking OFF command

[I◄◀] : Tracking OFF of surroundings on inside command

[I]~[9] : Servo relation examination command

[MENU] : Display of number of ROM

[TOP MENU] : Display of number of ROM

#### 5.Content of processing

(1) A reproduction and posed inside display the jitter measurement value and the value of the current of the laser on the FL display in the TEST mode.

| FIX4 | BYTE7  | Value of current of laser (subordinate position) |

|------|--------|--------------------------------------------------|

|      | BYTE8  | Value of current of laser (high rank)            |

|      | BYTE9  | Jitter measurement value (subordinate position)  |

|      | BYTE10 | Jitter measurement value (high rank)             |

|      |        |                                                  |

FL display

Value of current of laser

FL display(Example)

0033 0000

Remote control "4" button Value of current of laser for CD Remote control "5" button Value of current of laser for DVD

Value of current of laser

As for the value of the current of the laser, the figure displayed on the FL display reaches the current value as it is by the unit of mA.

It is 33mA if displayed as "0033". <For DVD>

If the value of the current of the laser is 64mA or less, it is possible to judge simply with about normal.

The deterioration of the laser diode of picking up is thought when there are 65mA or more value of the current of the laser.

<For CD>

If the value of the current of the laser is 49mA or less, it is possible to judge simply with about normal.

The deterioration of the laser diode of picking up is thought when there are 50mA or more value of the current of the laser.

Jitter measurement value

FL display(Example)

| 0033 20A2                | The jitter value is displayed by the hex |

|--------------------------|------------------------------------------|

| <b>f</b><br>jitter value |                                          |

<Please adjust when corresponding to the following.>

- When you exchange picking up.

- When you replace the spindle motor.

- When the reading accuracy of the signal is low.

(The screen sometimes stops in outer which with the block noise to the screen on the disk)

#### (2) EEPROM initialization

When the ENTER key is pushed in the test mode; Done the intialize for EEPROM of system CPU and unit CPU.

FL display

| Т | Е | S | Т |   |   |   | D | R | 2 |

|---|---|---|---|---|---|---|---|---|---|

|   |   | E | E | Р | R | 0 | М |   |   |

#### (3) Inside and outside surroundings tracking OFF

After searches for the DA disk to first TR and each last TR when "I I and the

" ►► I" key are pushed in the test mode, tracking OFF is processed.

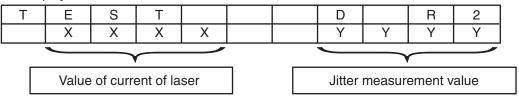

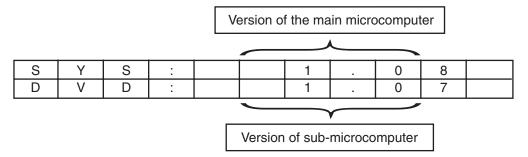

#### (4) Display of number of ROM

When MENU and the TOP MENU key are pushed in the test mode, the number of ROM of the main microcomputer, a sub-microcomputer, the unit microcomputer, and microcode is displayed on the FL display instead of the test display.

Transmission command: C2(ROM VERSION REQUEST) Data from unit CPU is as follows.

FIX4 BYTE11: Ver subordinate position byte of unit CPU BYTE12: Ver high-ranking byte of unit CPU (HEX) BYTE13: Date of microcode(ASCII)

FL display (When you press MENU:five seconds).

FL display (When you press TOP MENU: five seconds).

(5) Servo relation examination command

The following processing is done to ten keys in the test mode respectively.

- [1]: Start & reproduction of DISC (reproduction from starting position)

- [2]: TNO+1 search of CD

- [3]: TNO-1 search of CD

- [4] : The CD\_LD lighting (Turn off with the stop button).

- [5] : The DVD\_LD lighting (Turn off with the stop button).

- [6]: DVDx1.4 jitter measurement mode

- [7]: Unused

- [8] : The display (The address is done and -1 is done).

- [9] : The display (The address is done and +1 is done).

- ([8] and [9] are the stop button and Back to Top.)

# <Cassette mechanism section>

Recording and play head/Erase head

Mechanism control P.C. board

### ■Mechanism section

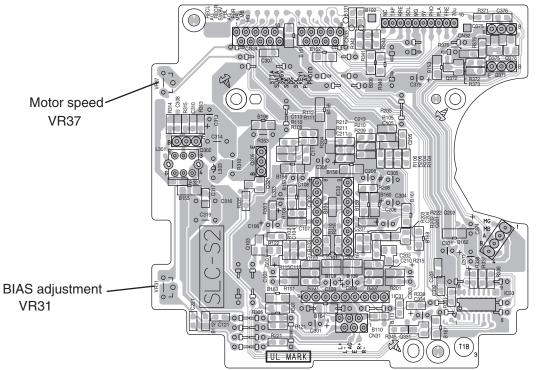

| Item                    | Confirmation of angle of head                                                                                                                                                                                                                                                                                                                                                         | Tape speed confirmation                                                                                                                                                      |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mesurement<br>condition | Test tape: VT703L (8kHz)<br>Measurement output terminal:<br>Speaker terminal                                                                                                                                                                                                                                                                                                          | Test tape: VT712 (3kHz)<br>Measurement output terminal:<br>Speaker terminal or headphone terminal                                                                            |

| Mesurement<br>procedure | <ol> <li>Test tape VT703L (8kHz) is played.</li> <li>It is adjusted that becomes an output<br/>that both are the maximum on a forward<br/>side and a reverse side with the screw<br/>for the azimuth adjustment.</li> <li>This adjustment is adjusted respectively<br/>with the adjustment screw for the forward<br/>side and the adjustment screw for a<br/>reverse side.</li> </ol> | Test tape VT712(3kHz) of the forward is<br>reproduced by finishing rolling , and<br>adjusted for the display of the frequency<br>counter to become 2,940-3,090Hz by<br>VR37. |

| Standard value          | The maximum output                                                                                                                                                                                                                                                                                                                                                                    | 2,940 ~ 3,090Hz                                                                                                                                                              |

| Adjustment position     | Only when the head is exchanged, adjusts.                                                                                                                                                                                                                                                                                                                                             | VR37                                                                                                                                                                         |

# ■Reference and standard value of confirmation matter

| Item                    | Forward/reverse tape speed difference                                                                                                          | Wow & flutter                                                                                                                                     |  |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Mesurement condition    | Test tape: VT712 (3kHz)<br>Measurement output terminal: Speaker terminal or headphone terminal                                                 |                                                                                                                                                   |  |  |

| Mesurement<br>procedure | Both reverse must forward/reproduce, and<br>the speed difference must be 6.0Hz or<br>less as for finish wrapping of test tape<br>VT712 (3kHz). | Both reverse must forward/reproduce,<br>and each wow & flutter must be 0.25%<br>(WRMS) or less as for begin to wrap of<br>test tape VT712 (3kHz). |  |  |

| Standard value          | 6.0Hz or less                                                                                                                                  | 0.25% or less (WRMS)                                                                                                                              |  |  |

| Adjustment position     | VR31                                                                                                                                           |                                                                                                                                                   |  |  |

# ■Electric adjustment

| Item                    | Recording BIAS adjustment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Recording reproduction<br>frequency characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mesurement<br>condition | Forward or reverse<br>Test tape: AC-514 TYPE II and<br>AC-225 TYPE I<br>Measurement output terminal:<br>Recording and headphone terminal                                                                                                                                                                                                                                                                                                                                                                                                  | Standard frequency: 1kHz/10kHz<br>(Srandard: -20dB)<br>Test tape: AC-514 TYPE II<br>Measurement input terminal: OSC IN                                                                                                                                                                                                                                                                                                                                                                  |

| Mesurement              | <ol> <li>Test tape (AC-514 TYPE II, AC-225<br/>TYPE I) is installed, and makes to<br/>recording/pose.</li> <li>Connects in the head for the recording<br/>and to connect 100 with the series and<br/>to measure the current of the bias,<br/>connects with VTVM.</li> <li>The pose is released after sets and the<br/>recording begins. It is adjusted that the<br/>current of the bias reaches the following<br/>value by VR31 for L side at this time and<br/>VR32 for R side.</li> <li>0 µ A (TYPE I) and4.20 µ A (TYPE II)</li> </ol> | <ol> <li>Test tape (AC-514 TYPE II) is installed,<br/>and makes to recording/pose.</li> <li>Records the recording's releasing the<br/>pose, beginning, and repeating 1kHz<br/>and 10kHz of a standard frequency from<br/>the frequency transmitter.</li> <li>VR31 for L side and VR32 for R side are<br/>adjusted so that the recorded part may<br/>be reproduced and there is a difference<br/>between 1kHz and 10kHz in 1dB }2dB,<br/>and the recording is repeated again.</li> </ol> |

| Standard value          | AC-225: 4.20 μ A<br>AC-514: 4.0 μ A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Output difference<br>1kHz/10kHz:-1dB±2dB                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Adjustment position     | VR3 <sup>-</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

# ■Electric characteristic confirmation

| Item                    | Current of recording bias                                                                                                                                                                                                                                                                    | Deletion current (standard value)                                                                                                                                                                                                                                                                                                 |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mesurement<br>condition | Forward or reverse<br>Test tape: AC-514 TYPE II<br>Measurement terminal:<br>BIAS TP on P.C.board                                                                                                                                                                                             | Forward or reverse<br>State of recording<br>Test tape: AC-514 TYPE II and<br>AC-225TYPE I<br>Measurement terminal:<br>Erase head's both ends                                                                                                                                                                                      |

| Mesurement<br>procedure | <ol> <li>It is confirmed that BIAS1 and 2 are<br/>switched, and the frequency changes.</li> <li>Test tape (AC-514 TYPE) is installed,<br/>and recording/makes to the pose.</li> <li>It is confirmed that it is BIAS TP on the<br/>substrate and the frequency is 100Hz±<br/>6kHz.</li> </ol> | <ol> <li>Test tape (AC-514 TYPE II) is installed,<br/>and makes to recording/pose.</li> <li>The pose is released and after sets in<br/>the state of the recording, 1W is<br/>confirmed, and connects with the series,<br/>and the deletion current is confirmed<br/>from erase head's both ends to the<br/>erase head.</li> </ol> |

| Standard<br>value       | $100 \text{kHz} \pm 6 \text{kHz}$                                                                                                                                                                                                                                                            | TYPE II : 120mA<br>TYPE I : 75mA                                                                                                                                                                                                                                                                                                  |

| Adjustment position     |                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                   |

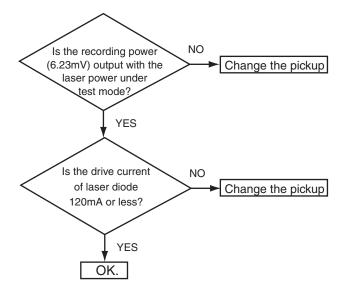

# Maintenance of MD pickup

#### 1. Cleaning of pickup lens

- (1) Prior to changing the pickup, clean the pickup lens.

- (2) For cleaning the lens, use the following cotton swab after mearsing it in alcohol.

Product No. JCB-B4; Manufacturer; Nippon Cotton Swab

- Confirmation of the service life of laser diode when the service life of the laser diode has been exhausted, the following symptoms will appear.

- (1) Recording will become impossible.

- (2) The RF output (EFM output and eye pattern amplitude) will become lower.

- (3) The drive current required for light emitting of laser diode will be increased.

Confirm the service life according to the following flow chart:

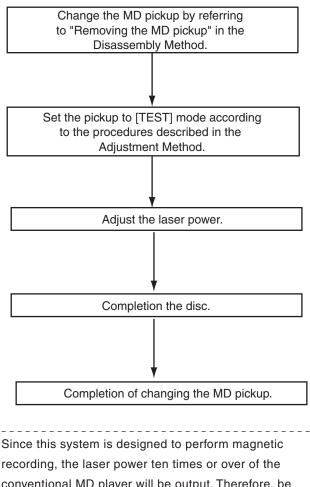

# Procedures of changing the MD pickup

recording, the laser power ten times or over of the conventional MD player will be output. Therefore, be sure to perform not only adjustment and operation of this system so carefully as not to directly look at the laser beam or touch on the body.

# 3. Method of measuring the drive current of laser diode

When the voltage measured at both side of R337 of the MD servo P.C. board have become 120mV or over, the service life of the laser diode is judged to have been exhausted.

# 4. Semi-solid state resistors on the APC P.C. board

The semi-solid state resistor on the APC P.C.board attached to the pickup is used for adjusting the laser power. Since these resistor should be adjusted in pair according to the characteristics of the optical block, be sure not to touch on the resistors.

Since the service life of the laser diode will be exhausted when the laser power is low, it is necessary to change the pickup. Meanwhile, do not pickup. Otherwise, the pickup will be damaged due to over current.

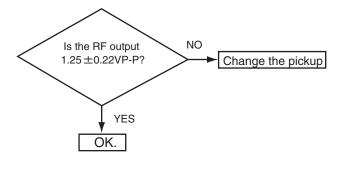

# Maintenance of DVD pickup

- 1. Cleaning of pickup lens

- (1) Prior to changing the pickup, clean the pickup lens.

- Confirmation of the service life of laser diode when the service life of the laser diode has been exhausted, the following symptoms will appear.

- (1) The RF output (EFM output and eye pattern amplitude) will become lower.

- (2) The drive current required for light emitting of laser diode will be increased.

Confirm the service life according to the following flow chart:

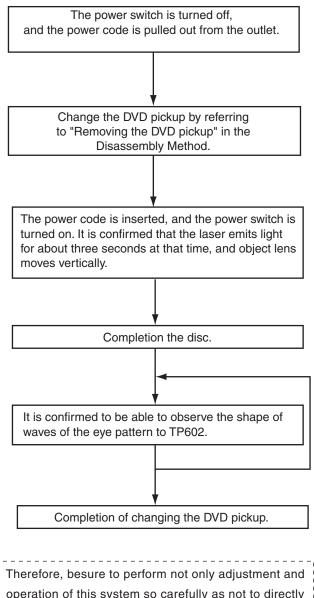

# Procedures of changing the DVD pickup

3. Semi-solid state resistors on the APC P.C. board

The semi-solid state resistor on the APC P.C.board attached to the pickup is used for adjusting the laser power. Since these resistor should be adjusted in pair according to the characteristics of the optical block, be sure not to touch on the resistors.

Since the service life of the laser diode will be exhausted when the laser power is low, it is necessary to change the pickup. Meanwhile, do not pickup. Otherwise, the pickup will be damaged due to over current.

operation of this system so carefully as not to directly look at thelaser beam or touch on the body.

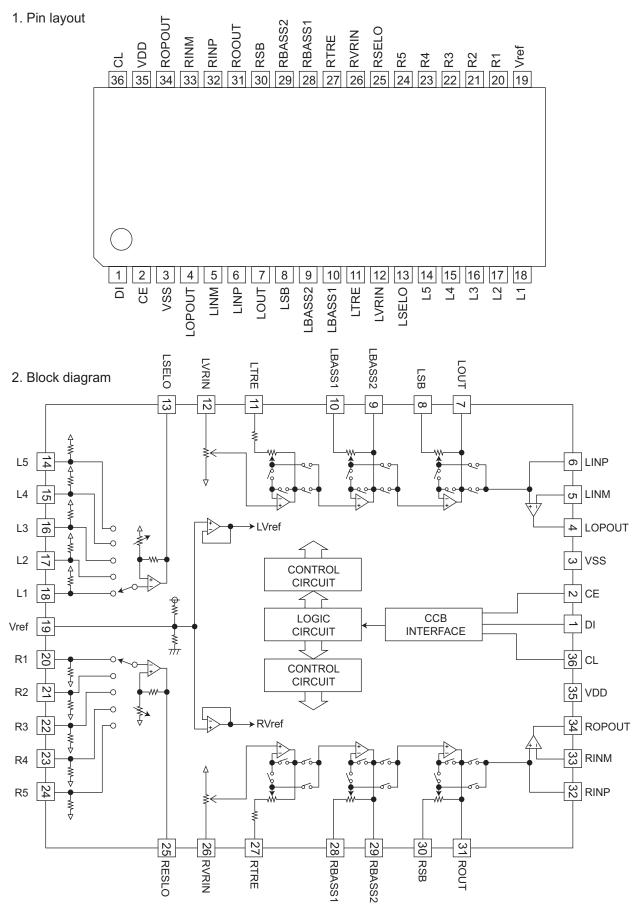

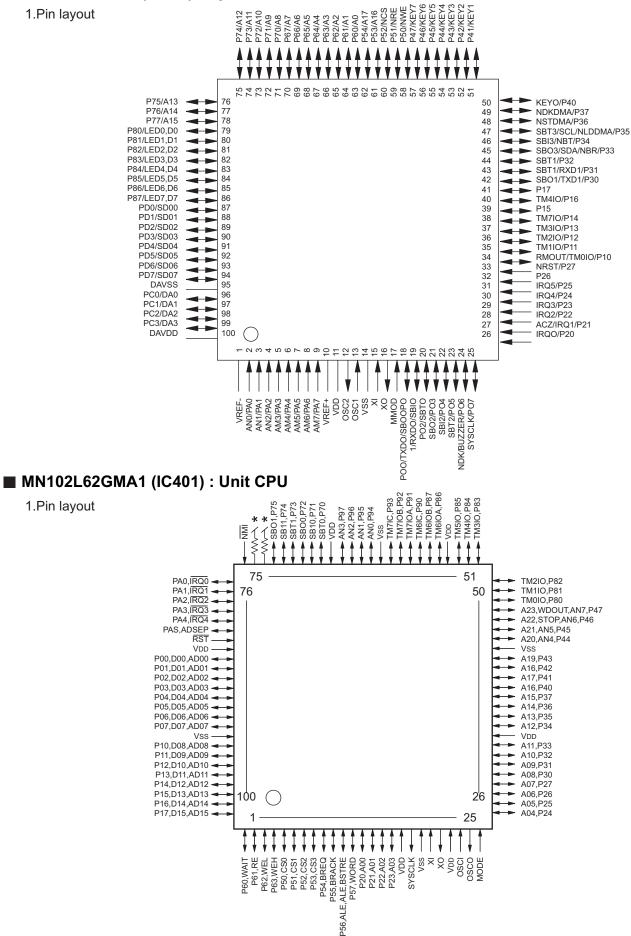

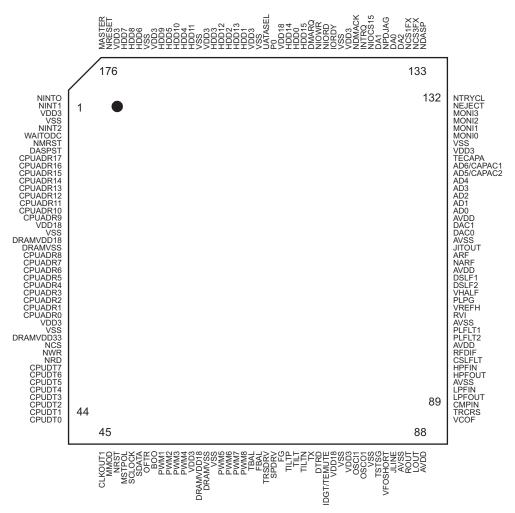

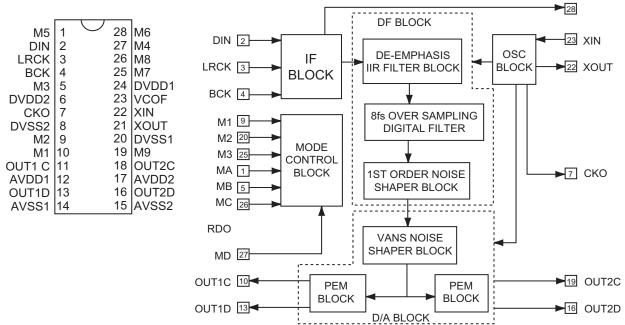

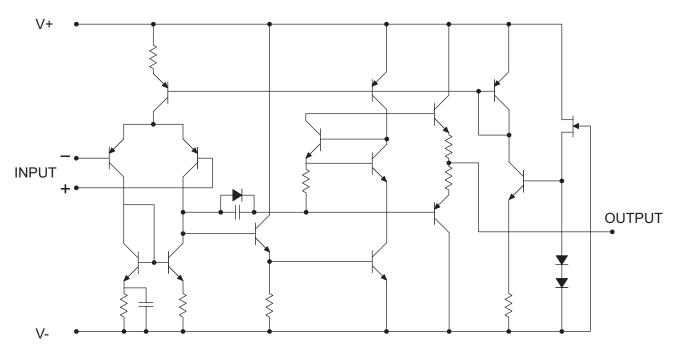

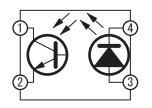

# **Description of major ICs**

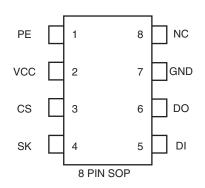

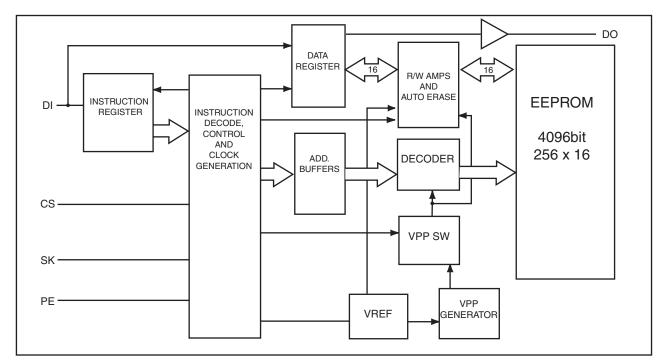

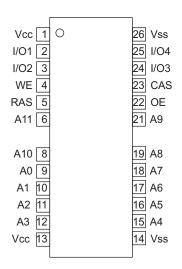

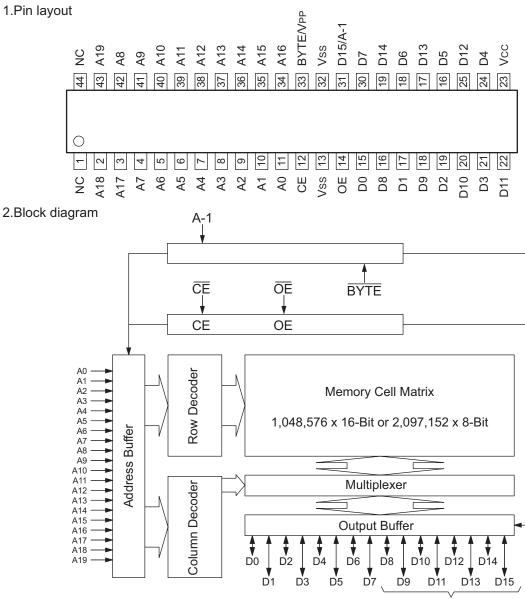

# AK93C65AF-X (IC451) : EEPROM

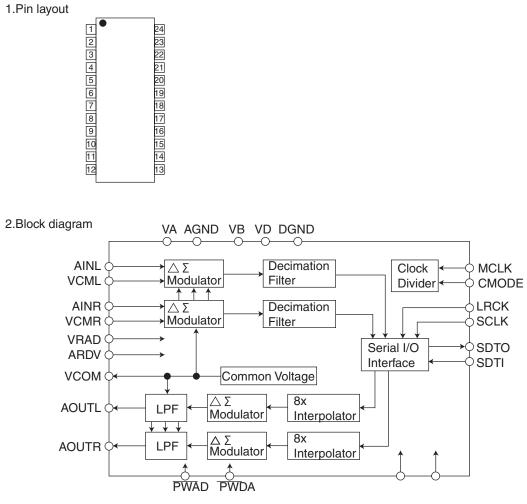

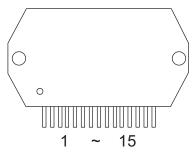

1.Pin layout

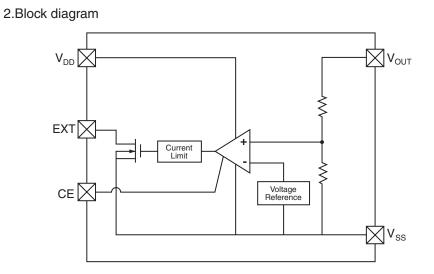

#### 2.Block diagram

#### 3.Pin function

| Pin no. | Symbol | Function                                        |

|---------|--------|-------------------------------------------------|

| 1       | PE     | Program enable (With built-in pull-up resistor) |

| 2       | VCC    | Power supply                                    |

| 3       | CS     | Chip selection                                  |

| 4       | SK     | Cereal clock input                              |

| 5       | DI     | Cereal data input                               |

| 6       | DO     | Cereal data output                              |

| 7       | GND    | Ground                                          |

| 8       | NC     | No connection                                   |

NOTE : The pull-up resistor of the PE pin is about 2.5M  $\ensuremath{\Omega}$  (VCC=5V)

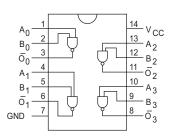

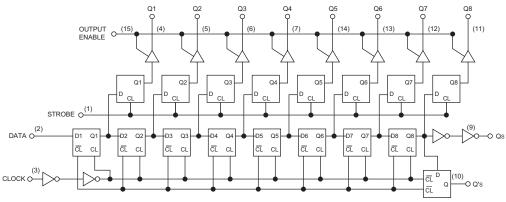

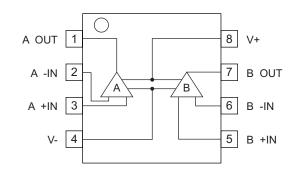

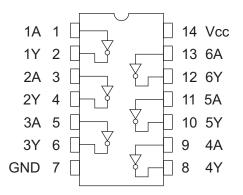

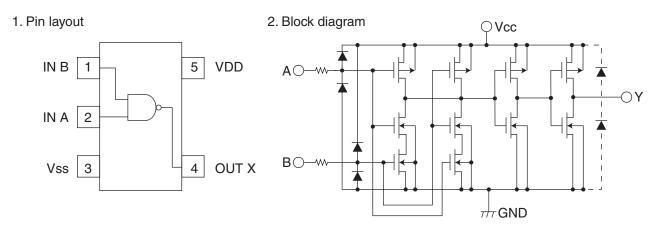

# **74VHC00MTC-X (IC455,503) : NAND gate**

1.Pin layout / Block diagram

**Truth Table**

Truth Table

CLR  $\overline{PR}$

> L н Х

н L Х Х

L L

Н Н

Н Н Н ~

н Н Х  $\overline{}$

Inputs

D СК

Х Х

L

Х

~

set and clear inputs return to their inactive (HIGH) state

Outputs

H(Note 1) H(Note 1)

Q

L

Н

L

Н

Note 1: This configurailon is nonstable; that is, it will not persist when pre-

Qn

Q

Н

L

Н

L

Qn

Function

Clear

Preset

No Change

| А | В | ō |

|---|---|---|

| L | L | Н |

| L | Н | Н |

| Н | L | Н |

| Н | Н | L |

#### 2.Pin function

| Pin Names                      | function |

|--------------------------------|----------|

| A <sub>n'</sub> B <sub>n</sub> | Inputs   |

| ō <sub>n</sub>                 | Outputs  |

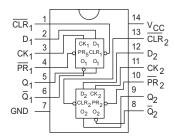

# ■ 74VHC74MTC-X (IC454) : Dual D-type Flip-Flop with preset and clear

1.Pin layout / Block diagram

#### 2.Pin function

| Pin Names                                     | function             |

|-----------------------------------------------|----------------------|

| D <sub>1'</sub> D <sub>2</sub>                | Data Inputs          |

| СК <sub>1'</sub> СК <sub>2</sub>              | Clock Pulse Inputs   |

| CLR <sub>1'</sub> CLR <sub>2</sub>            | Direct Clear Inputs  |

| PR <sub>1'</sub> PR <sub>2</sub>              | Direct Preset Inputs |

| $Q_{1'} \overline{Q}_{1'} Q_2 \overline{Q}_2$ | Output               |

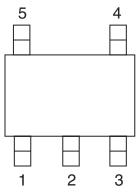

### BR93LC66F-X (IC590):EEPROM

NC 8

7

6

5 DI

GND

DO

#### 1.Terminal layout

1

2

NC

VCC

CS 3

SK 4

2.Pin Functions

|      | 2.1 111 011000 | 113 |                                             |

|------|----------------|-----|---------------------------------------------|

|      | Symbol         | I/O | Function                                    |

|      | VCC            | -   | Power supply                                |

| )    | GND            | -   | Connect to GND                              |

|      | CS             | I   | Chip select input                           |

|      | SK             | I   | Serial clock input                          |

|      | DI             | I   | Start bit,OP-code,address,serial data input |

| DO O |                | 0   | Serial data output,                         |

|      |                |     | Internal state display output of READY/BUSY |

#### AK4519VF-X (IC480) : A / D.D / A converter

| Pin<br>NO. | Symbol | I/O | Function                                |

|------------|--------|-----|-----------------------------------------|

| 1          | VRDA   | I   | Voltage Reference Input Pin for DAC, VA |

| 2          | VRAD   | Ι   | Voltage Reference Input Pin for ADC, VA |

| 3          | AINR   | Ι   | RCH Analog Input Pin                    |

| 4          | VCMR   | 0   | Rch Common Voltage Output Pin, 0.45xVA  |

| 5          | VCML   | 0   | Lch Common Voltage Output Pin, 0.45xVA  |

| 6          | AINL   | Ι   | Lch Analog Input Pin                    |

| 7          | PWAD   | Ι   | ADC Power-Down Mode Pin "L":Power Down  |

| 8          | PWDA   | Ι   | DAC Power-Down Mode Pin "L":Power Down  |

| 9          | MCLK   | Ι   | Master Clock Input Pin                  |

| 10         | LRCK   | Ι   | Input/Output Channel Clock Pin          |

| 11         | SCLK   | Ι   | Audio Serial Data Clock Pin             |

| 12         | SDTO   | 0   | Audio Serial Data Output Pin            |

| 13         | DGND   | -   | Digital Ground Pin                      |

| 14         | VD     | -   | Digital Power Supply Pin                |

| 15         | SDTI   | I   | Audio Serial Data Input Pin             |

| 16         | CMODE  | I   | Master Clock Select Pin                 |

| 17         | DEM1   | I   | De-emphasis Frequency Select Pin        |

| 18         | DEM0   | I   | De-emphasis Frequency Select Pin        |

| 19         | AOUTL  | 0   | Lch Analog Output Pin                   |

| 20         | AOUTR  | 0   | Rch Analog Output Pin                   |

| 21         | VCOM   | 0   | Common Voltage Output Pin, 0.45xVA      |

| 22         | AGND   | -   | Analog Ground Pin                       |

| 23         | VB     | -   | Substrate Pin                           |

| 24         | VA     | -   | Analog Power Supply Pin                 |

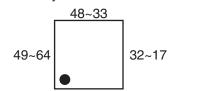

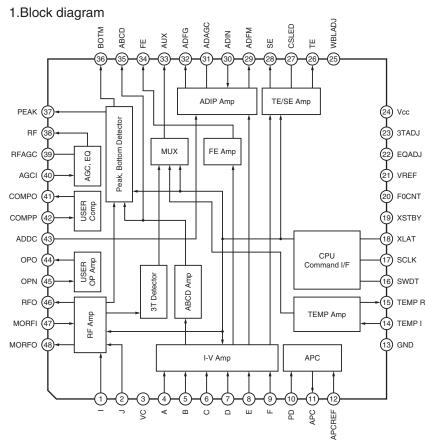

#### AN8703FH-V (IC101) : Front-end processor for DVD

| 3.Pin | function |

|-------|----------|

|-------|----------|

| Pin No. | Symbol   | Function                      |

|---------|----------|-------------------------------|

| 1       | LPC1     | Laser pin input (DVD head)    |

| 2       | LPCO1    | Laser drive output (DVD head) |

| 3       | LPC2     | Laser pin input (CD head)     |

| 4       | LPCO2    | Laser drive output (CD head)  |

| 5       | VFOSHORT | VFOSHORT control              |

| 6       | TBAL     | Tracking balance control      |

| 7       | FBAL     | Focus balance control         |

(1/2)

| Pin No. | Symbol         | Function                                       |

|---------|----------------|------------------------------------------------|

| 8       | POFLT          | Tracking detection threshold level             |

| 9       | DTRD           | Data slice data read signal input (for RAM)    |

| 10      | IDGT           | Data slice address gate signal input (for RAM) |

| 11      | STANBY         | Standby mode control                           |

| 12      | SEN            | SEN (serial data input)                        |

| 13      | SCK            | SCK (serial data input)                        |

| 14      | STDI           | STDI (serial data I/o)                         |

| 15      | RSCL           | Reference current supply                       |

| 16      | JLINE          | J-line current setting                         |

| 17      | TEN            | Tracking error amplifier inverted input        |

| 18      | TEOUT          | Tracking error signal output                   |

| 19      | AGCBAL         | Offset adjustment for DRC - 1                  |

| 20      | ASOUT          | Full addition signal output                    |

| 21      | FEN            | Focus error amplifier inverted input           |

| 22      | FEOUT          | Focus error signal output                      |

| 23      | AGCOFST        | Offset adjustment for DRC - 2                  |

| 24      | MON            | Monitor                                        |

| 25      | AGCLVL         | Output amplitude adjustment for DRC            |

| 26      | GND2           | Ground 2                                       |

| 27      | VREF2          | VREF2 voltage output                           |

| 28      | VCC2           | Power supply 2 (5V)                            |

| 29      | VHALF          | VHALF voltage output                           |

| 30      | DFLTON         | Filter amplifier inverted output               |

| 31      | DFLTOP         | Filter amplifier positive output               |

| 32      | DCFLT          | Filter output capacitance connection           |

| 33      | GND3           | Ground3                                        |

| 34      | RFDIFO         | Radial differential output                     |

| 35      | RFOUT          | RF full-addition amplifier output              |

| 36      | VCC3           | Power supply 3 (3.3V)                          |

| 37      | RFC            | Filter for RF-group delay correction amplifier |

| 38      | DCRF           | DC-cut filter for RF full-addition amplifier   |

| 39      | OFTR           | OFTR output                                    |

| 40      | BDO            | BDO output                                     |

| 41      | RFENV          | RF envelope output                             |

| 42      | BOTTOM         | Bottom envelope detection filter               |

| 43      | PEAK           | Peak envelope detection filter                 |

| 44      | AGCG           | AGC amplifier gain control                     |

| 45      | AGCO           | AGC amplifier level control                    |

| 46      | TESTSG         | TEST signal input                              |

| 47      | RFINP          | RF signal positive input                       |

| 48      | RFINN          | RF signal inverted input                       |

| 49      | VIN5           | Internal four-partition (CD) RF input 1        |

| 50      | VIN6           | Internal four-partition (CD) RF input 2        |

| 51      | VIN7           | Internal four-partition (CD) RF input 3        |

| 52      | VIN7<br>VIN8   | Internal four-partition (CD) RF input 4        |

| 53      | VIN9           | External two-partition (DVD) RF input 2        |

| 54      | VIN10          | External two-partition (DVD) RF input 1        |

| 55      | VICC1          | Power supply 1 (5V)                            |

| 56      | VREF1          | VREF1 voltage output                           |

| 57      | VIN1           | Internal four-partition (DVD) RF input 1       |

| 58      | VIN1<br>VIN2   | Internal four-partition (DVD) RF input 2       |

| 59      | VIN2<br>VIN3   | Internal four-partition (DVD) RF input 2       |

| 60      | VIN3<br>VIN4   | Internal four-partition (DVD) RF input 3       |

| 61      | GND1           | Ground 1                                       |

| 62      | VIN11          | 3-beam sub (CD) input 2                        |

| 63      | VIN11<br>VIN12 | 3-beam sub (CD) input 2                        |

| 00      | VINIZ          |                                                |

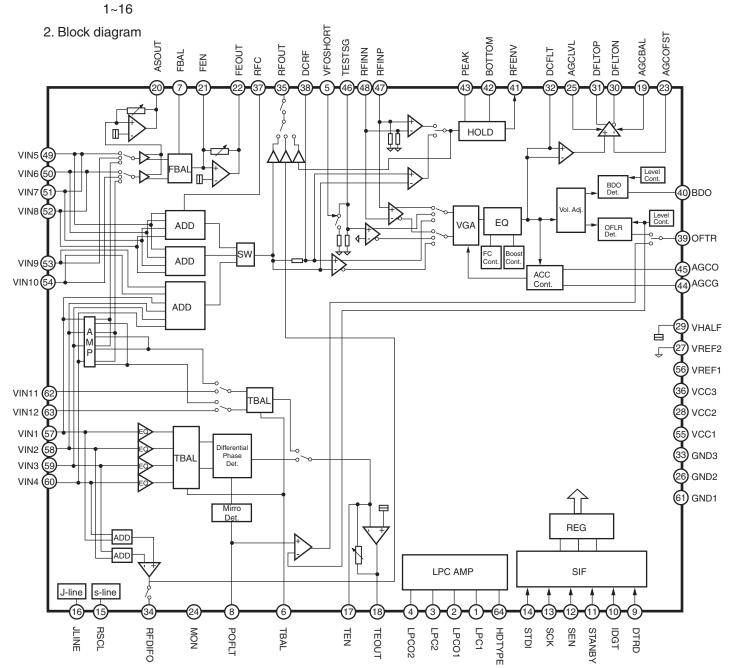

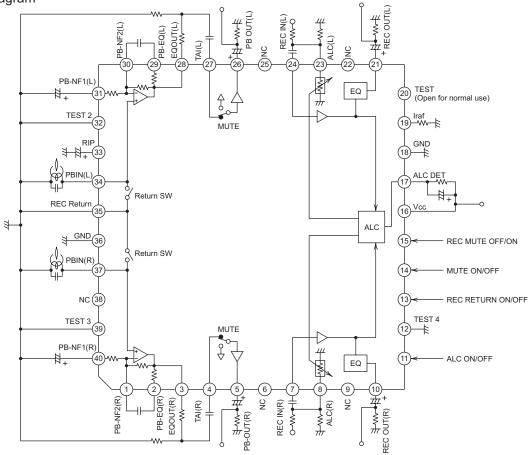

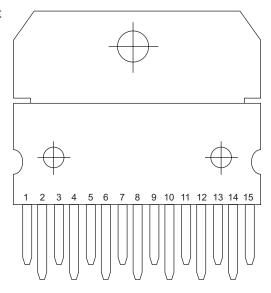

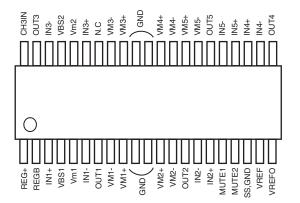

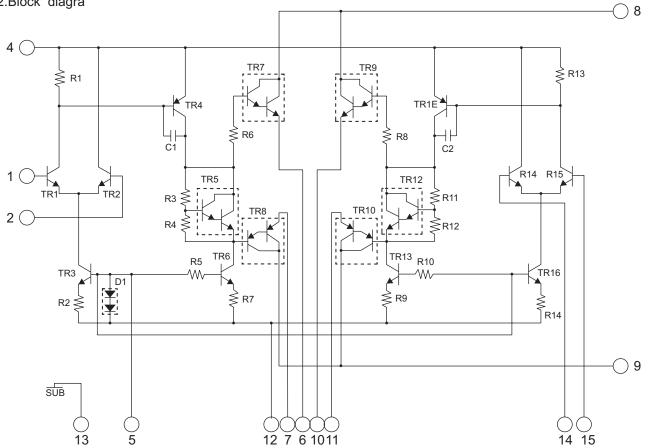

# BA5983FM-X (IC201) : Driver

1.Pin layout / Block diagram

| No. | Symbol   | Function                           | No. | Symbol   | Function                           |

|-----|----------|------------------------------------|-----|----------|------------------------------------|

| 1   | BIAS IN  | Input for Bias-amplifier           | 15  | VO4(+)   | Non inverted output of CH4         |

| 2   | OPIN1(+) | Non inverting input for CH1 OP-AMP | 16  | VO4(-)   | Inverted output of CH4             |

| 3   | OPIN1(-) | Inverting input for CH1 OP-AMP     | 17  | VO3(+)   | Non inverted output of CH3         |

| 4   | OPOUT1   | Output for CH1 OP-AMP              | 18  | VO3(-)   | Inverted output of CH3             |

| 5   | OPIN2(+) | Non inverting input for CH2 OP-AMP | 19  | PowVcc2  | Vcc for CH3/4 power block          |

| 6   | OPIN2(-) | Inverting input for CH2 OP-AMP     | 20  | STBY2    | Input for CH4 stand by control     |

| 7   | OPOUT2   | Output for CH2 OP-AMP              | 21  | GND      | Substrate ground                   |

| 8   | GND      | Substrate ground                   |     | OPOUT3   | Output for CH3 OP-AMP              |

| 9   | STBY1    | Input for CH1/2/3 stand by control | 23  | OPIN3(-) | Inverting input for CH3 OP-AMP     |

| 10  | PowVcc1  | Vcc for CH1/2 power block          | 24  | OPIN3(+) | Non inverting input for CH3 OP-AMP |

| 11  | VO2(-)   | Inverted output of CH2             | 25  | OPOUT4   | Output for CH4 OP-AMP              |

| 12  | VO2(+)   | Non inverted output of CH2         | 26  | OPIN4(-) | Inverting input for CH4 OP-AMP     |

| 13  | VO1(-)   | Inverted output of CH1             | 27  | OPIN4(+) | Non inverting input for CH4 OP-AMP |

| 14  | VO1(+)   | Non inverted output of CH1         | 28  | PreVcc   | Vcc for pre block                  |

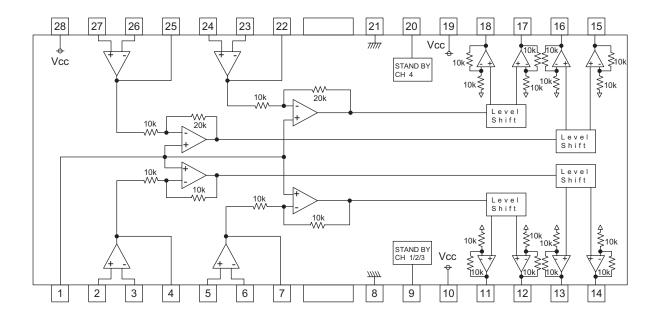

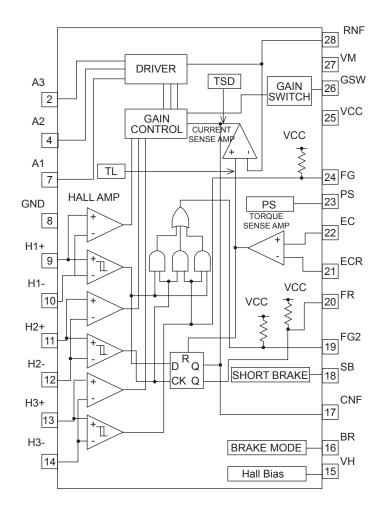

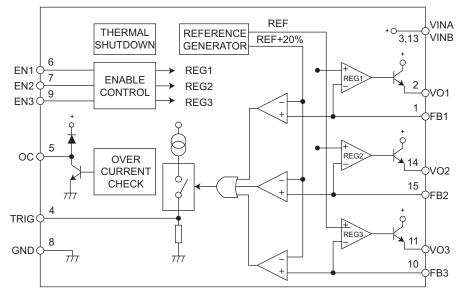

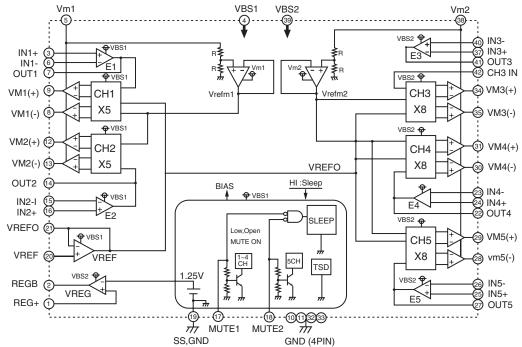

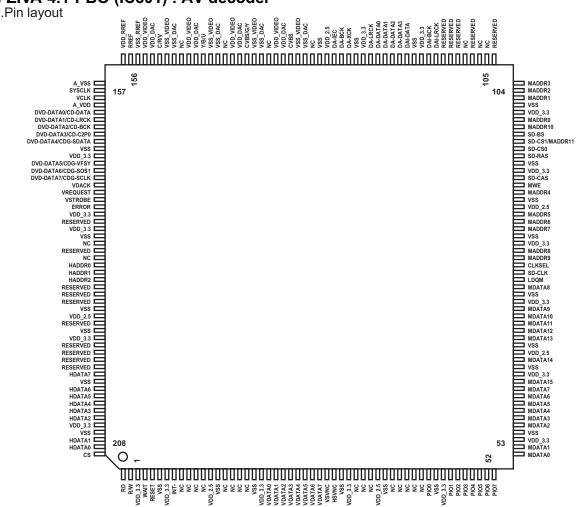

## BA6664FM-X (IC251) : Motor driver

1. Block diagram

| Pin No. | Symbol | Function                           | Pin No. | Symbol | Function                               |

|---------|--------|------------------------------------|---------|--------|----------------------------------------|

| 1       | NC     | NC                                 | 19      | FG2    | 3Phase synthesized FG signal           |

| 2       | A3     | Output3 for motor                  |         |        | output terminal                        |

| 3       | NC     | NC                                 | 20      | FR     | Rotation detect signal output terminal |

| 4       | A2     | Output2 for motor                  | 21      | ECR    | Torque control standard voltage input  |

| 5       | NC     | NC                                 |         |        | terminal                               |

| 6       | NC     | NC                                 | 22      | EC     | Torque control voltage input terminal  |

| 7       | A1     | Output1 for motor                  | 23      | PS     | START/STOP switch                      |

| 8       | GND    | GND                                | 24      | FG     | FG signal output terminal              |

| 9       | H1+    | Positive input for hall input Amp1 | 25      | Vcc    | Power supply for signal division       |

| 10      | H1-    | Negative input for hall input Amp1 | 26      | GSW    | Gain switch                            |

| 11      | H2+    | Positive input for hall input Amp2 | 27      | VM     | Power supply for driver division       |

| 12      | H2-    | Negative input for hall input Amp2 | 28      | RNF    | Resistance connection pin for output   |

| 13      | H3+    | Positive input for hall input Amp3 |         |        | current sense                          |

| 14      | H3-    | Negative input for hall input Amp3 | FIN     | FIN    | GND                                    |

| 15      | VH     | Hall bias terminal                 |         |        |                                        |

| 16      | BR     | Brake Mode terminal                |         |        |                                        |

| 17      | CNF    | Capacitor connection pin for       |         |        |                                        |

|         |        | phase compensation                 |         |        |                                        |

| 18      | SB     | Short brake terminal               |         |        |                                        |

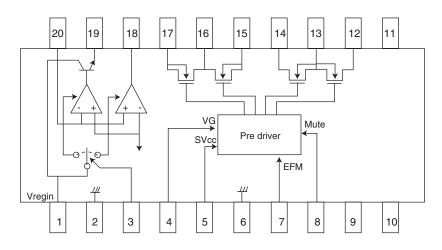

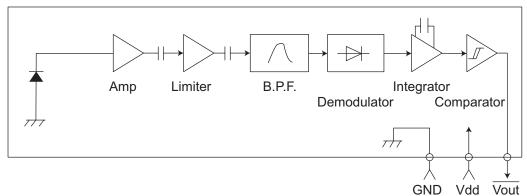

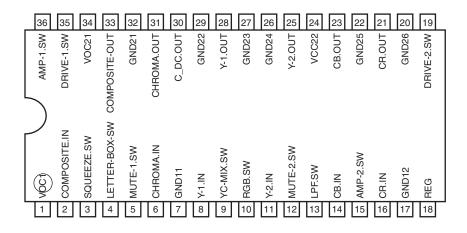

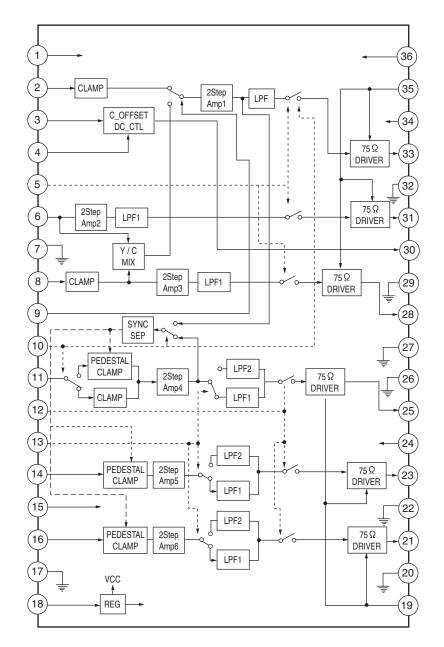

# BD7910FV-X (IC450) : M.HEAD driver

1.Block diagram

| Pin<br>No. | Symbol  | I/O | Function Pin No. Sy               |    | Symbol  | I/O | Function                                  |

|------------|---------|-----|-----------------------------------|----|---------|-----|-------------------------------------------|

| 1          | Vreg IN | Ι   | Regulator input and regulator     | 11 | NC      | -   | Non connect                               |

|            |         |     | power supply                      | 12 | VOD2    | 0   | Sync.output (Lower power MOS,drain)       |

| 2          | Reg GN  | -   | Regulator GND                     | 13 | VSS     | -   | "H"bridge GND (Lower power MOS,source)    |

| 3          | NC      | -   | Non connect                       | 14 | VOD1    | 0   | Sync.output (Lower power MOS,drain)       |

| 4          | VG      | Ι   | Voltage input for power MOS drive | 15 | VOS1    | 0   | Source output (Upper power MOS,source)    |

| 5          | SVCC    | 0   | EFM high level output voltage     |    | VDD     | -   | "H" bridge power supply terminal          |

| 6          | PDGND   | -   | Pre-driver GND                    |    |         |     | (Upper power MOS,source)                  |

| 7          | EFM     | Ι   | EFM signal input                  | 17 | VOS2    | 0   | Source output (Upper power MOS,source)    |

| 8          | MUTE    | Ι   | Mute control (Low active)         | 18 | Reg DRV | 0   | External PNP drive output for regulator   |

| 9          | NC      | 0   | Non conncet                       | 19 | Reg OUT | 0   | Reglator output (Emitter follower output) |

| 10         | NC      | 0   | Non connect                       | 20 | Reg NF  | -   | Regulator feedbaack terminal              |

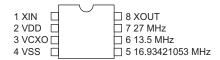

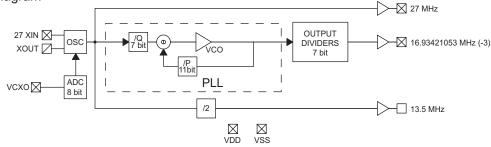

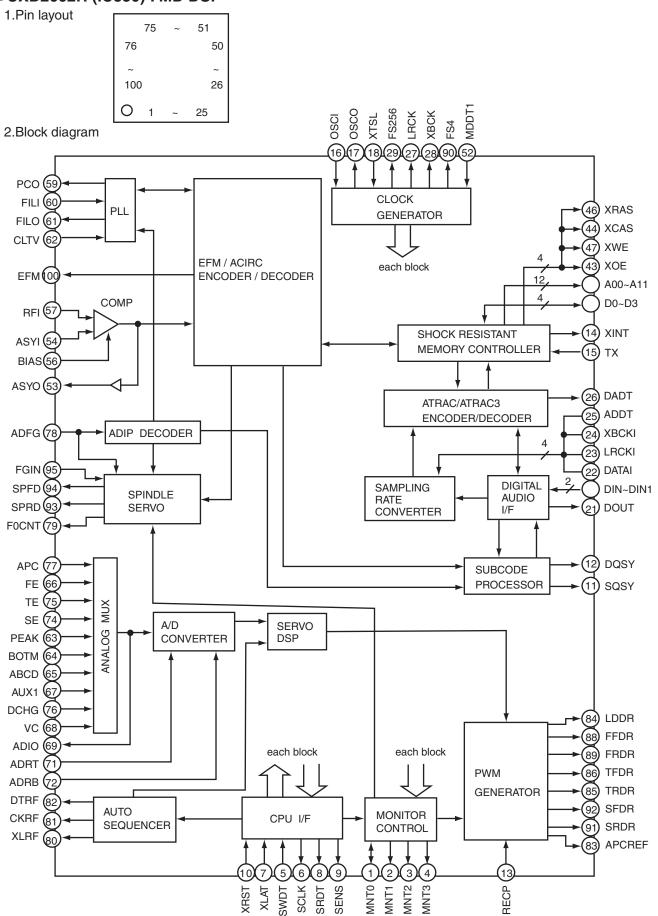

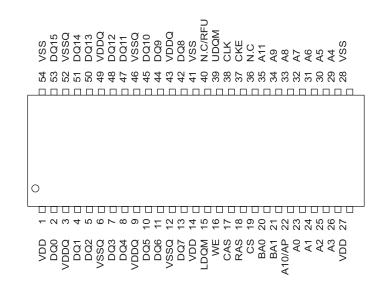

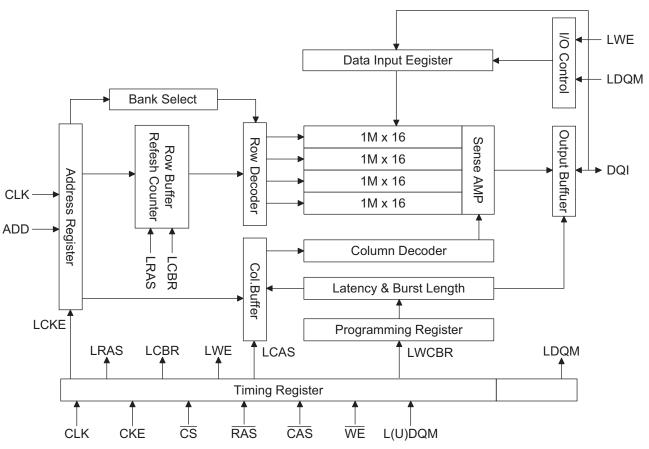

# CS5960AT-X (IC571) : MPEG/Audio clock generator with VCXO

1.Pin layout

#### 2.Block diagram

#### 3.Pin function

| No. | Symbol          | Function                      |

|-----|-----------------|-------------------------------|

| 1   | XIN             | Reference Crystal Input       |